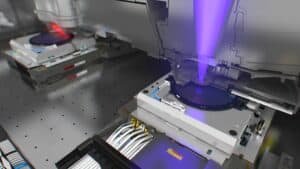

キヤノンが先日発表した、新たなナノインプリントリソグラフィ(NIL)装置「FPA-1200NZ2C」は、半導体業界の勢力図を一変する物になるかも知れない。

キヤノンが開発したナノインプリントリソグラフィ(NIL)技術は、5nmクラスのプロセス技術におけるチップ製造に使用可能であり、現在主流の極端紫外線(EUV)リソグラフィ装置と競合する可能性がある事は、製品発表時から指摘されていた。具体的な価格がどの程度になるのかは明らかにされていなかったが、どうやらEUVリソグラフィ装置に比べてかなり安価になるようだ。

Bloombergのインタビューにおいて、キヤノン会長兼社長兼最高経営責任者(CEO)の御手洗冨士夫氏は、NIL装置の価格について、EUVリソグラフィ装置と比較し「EUVに比べて全然安い。1桁違う」と述べ、「存在価値が非常にある」と述べている。実際に既に引き合いがあることも示唆した。

この技術は、特に資金面で制約がある小規模なチップメーカーにとって、先進的なチップ生産へのアクセスを広げることができると期待されている。

EUVシステムは200億円以上のコストがかかるのに対し、御手洗氏の主張が正しければ、NIL装置は20億円程度になる可能性がある。この低価格化により、先進的な生産ノードでのチップ製造がより手軽になる可能性がある。しかし、キヤノン自身もNIL技術が従来のEUVやDUVスキャナーを完全に置き換えるとは見ていない。「ASMLをひっくり返そうなんて大きなことは考えていない」と、御手氏は述べている。

従来のフォトリソグラフィシステムは、フォトマスクを介してウェハー上のレジスト層に回路パターンを投影するが、NIL技術は、回路設計が施された型を直接ウェハー上のレジストに押し付けることでパターンを転写する。この方法は、光学システムを介さずに行われるため、より精密な回路パターンの複製が可能であるとされる。NILは理論上、一度に複雑な2Dまたは3Dの回路パターンを作成できるため、生産コストの削減も期待出来る。ただし、NILはシリアルプロセスであり、フォトリソグラフィに比べてプロセス速度が遅い可能性がある。

NILの課題の一つは、型と基板の間の直接接触によって欠陥が生じやすいことだ。型や基板上の粒子や不純物が製造プロセスに欠陥をもたらし、収率や信頼性に影響を与える可能性がある。これを防ぐためには、厳格なプロセス管理と超清浄な環境が必要とされる。

地政学的な緊張の高まりにより、ASMLのEUVおよび先進的なDUVシステムの中国への輸出が禁止されたことは、キヤノンのNIL技術にとって潜在的な市場を生み出す可能性がある。ただし、14nm以下のチップの生産を可能にするツールの中国への輸出は、日本政府からの輸出ライセンスが必要となるため、同社は現実的ではないと述べている。

Source

- Bloomberg: キヤノン御手洗氏、ナノインプリント装置はEUVより「1桁」安い

- Tom’s Hardware: Canon’s Nanoimprint Litho Tool Could Disrupt Wafer Fab Equipment Market

コメントを残す