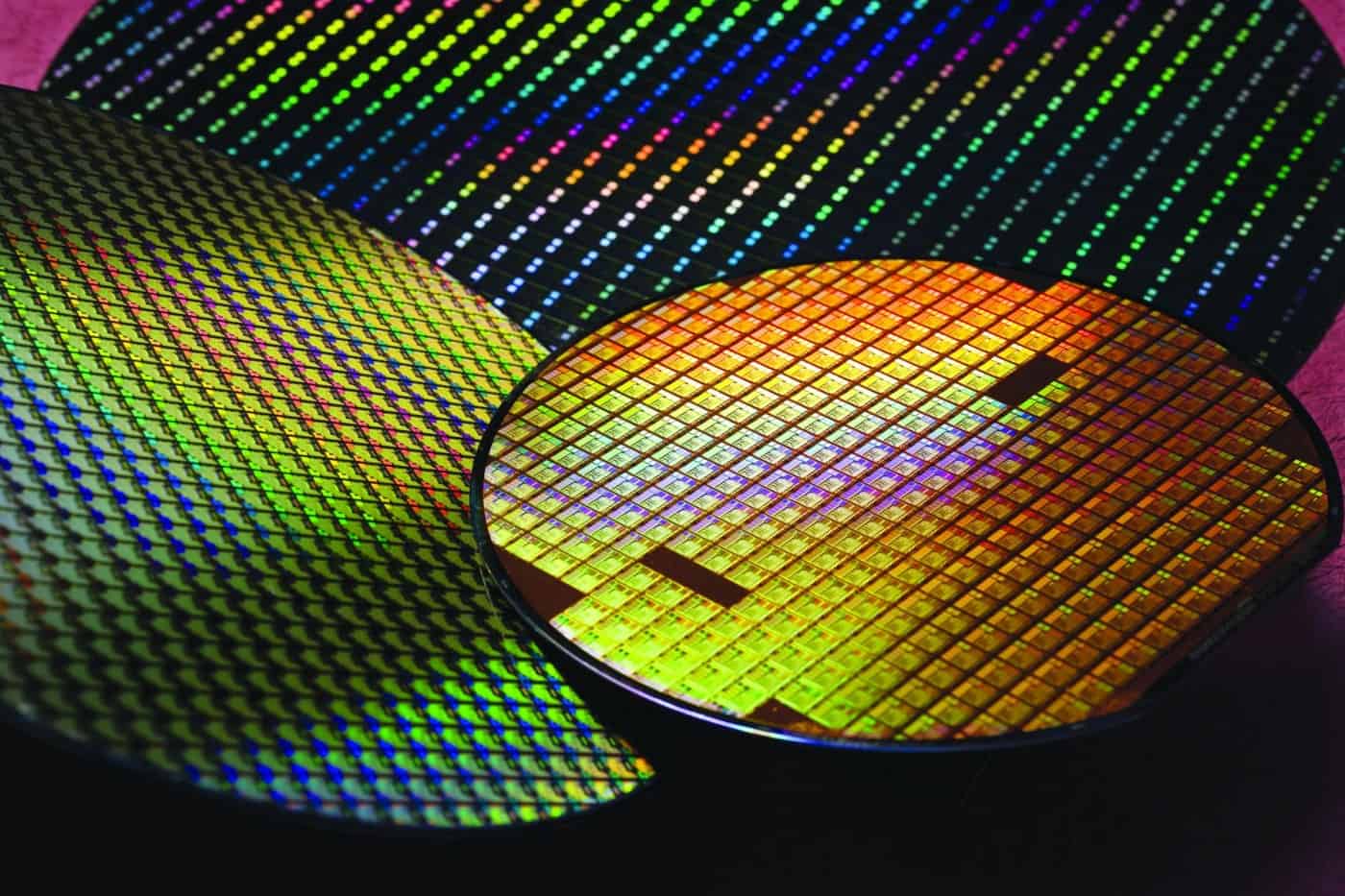

TSMCは、昨年末に3nmプロセスの量産を開始したばかりだが、この同社の最先端プロセスの歩留まり率について、Business Nextは、様々な業界のアナリストや専門家への取材した結果、他社と比較して劇的に優れている可能性があると報告している。

3nmプロセスでの量産開始については、ライバルのSamsungが先行して行っている。同社の3nmプロセスは、TSMCと比較して、GAA FETを採用するなど特筆すべき点があるが、その歩留まり率についてはあまり芳しくないとも報じられていた。

今回のTSMCによる3nmプロセス量産開始に伴って、Business Nextでは、様々な業界専門家に取材を行ったが、現時点ではTSMCのN3の歩留まり率は60%〜70%との見方が多いとのことだ。だが、75%〜80%と高くなる可能性があり、最初のロットとしてはかなり良好であると推定している。一方、金融アナリストのDan Nystedt氏は、TSMCの現在のN3歩留まりは、立ち上げ初期のN5歩留まりに似ており、メディアによると、80%にもなる可能性があるとツイートしている。

これに対し、Samsung Foundryの初期段階での3nmプロセスの歩留まり率は10%から20%とばらつきがあり、改善されていないと、業界筋の情報を引用している。

ただし、現在のTSMCのN3歩留まりについては、いくつか注意すべき点がある。まず、歩留まりがTSMCのFab18を流れる商用ウェハーに対して算出されているのか、TSMCの顧客の各種IPを含む商用ウェハーとシャトル(テスト)ウェハーに対して算出されているのかがわからないことだ。第二に、TSMCとその顧客以外は、現時点では、商用ウェハーとシャトルウェハーのどちらについても正確な歩留まり率を把握していない。第三に、商業用ウェハーに限って言えば、市場の噂に基づくものではあるが、今のところTSMCのN3はアーリーアダプター向けのごく限られたデザインの製造に使われている。

TSMCは、最大の顧客であり、最先端ノードのアルファクライアントであるAppleの要求を念頭に置いて最先端生産技術を開発する傾向があり、AppleはTSMCの能力に合わせてデザインを調整するので、初期の歩留まり率が80%というのもおかしなものではないだろう。ただし、大量生産される製品に搭載されるチップの歩留まり率が60%というのは、決して高いとは言えないかも知れない。

いずれにせよ、TSMCが商業的に生産するN3デザインの数は今のところ限られており、歩留まり関連のデータはファウンドリおよびその顧客の企業秘密であるため、TSMCのN3歩留まりが高いか低いかを判断することはできない。

実際、同じ理由で、TSMCのN3の歩留まりとSamsung Foundryの3GAE歩留まりを初期段階で比較することも控えている。

さらに、初期のN3ノード(別名N3B)にまつわる噂を念頭に置くと、他の開発者はプロセスウィンドウが改善されたN3Eを使うことになっているので、Appleだけがこの技術を全く採用しない可能性もある。一方、初期のN3歩留まりは、N3E(およびそのN3技術のファミリーの他のノード)には当てはまらない可能性があり、このN3Eの方こそが、今後メインで多くの企業に使用される予定なので、実際には業界全体が気にする必要があるものである。

現代の半導体製造技術は、何千ものプロセス工程を含み、材料、使用する製造装置ツール、プロセスレシピ、その他多くの要因に依存している。したがって、歩留まりを向上させたり低下させたりする方法は何千通りもあり、ある要因が他の要因にどのように影響するかを非常に深く理解することが重要である理由である。TSMCのN3(N3B)、N3E、N3S、N3P、N3Xは非常に異なる製造技術なので、初期のN3の歩留まりは他のノードにとって良い兆候だが、他のノードが同様に成功する(または成功しない)ことを保証するものではない。

Source

- Business Next: 台積電3奈米「近8成良率」狠甩三星!良率提升關鍵,藏在1000道魔鬼細節裡

- via Tom’s Hardware: Analysts Estimate TSMC’s 3nm Yields Between 60% and 80%

コメントを残す