コンピューターチップの基本的な構成要素の一つ、「トランジスタ」に10年に一度の大きな技術的革新が起きようとしている。この技術は、今後の半導体業界の勢力図を塗り替える可能性があるほど大きな変化をもたらすと言われている。

その技術は、トランジスタの設計にかかわる物だ。これまでの構造から大きく進化したこの設計は、「GAA(Gate All Around)」構造と呼ばれる。既存の設計よりも性能と効率が大幅に向上し、多くの高性能製品の競争力が変わる可能性があると言われる「GAA」を実現するために、Intel、Samsung、そしてTSMCは莫大な投資を行っているのだ。では、GAAとは一体どういった構造なのだろうか?

目次

「FinFET」による微細化の限界が見えてきた

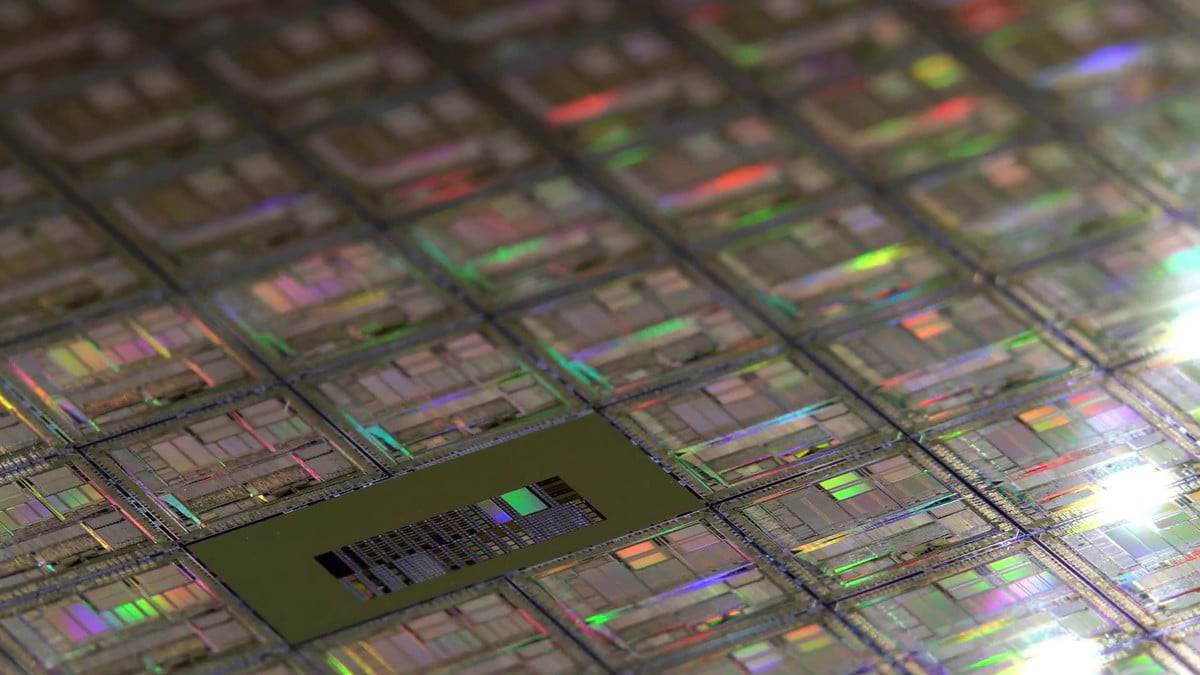

電子製品の多くに使われている「集積回路」は数多くのトランジスタを詰め込んだ物である。トランジスタは、超小型のスイッチとしての役割を担い、ON/OFFで「0と1」を表すことによって、2進法によるコンピューターの処理を実現している。このトランジスタが複数組み合わせられることで、「NOT・OR・AND」などの処理を行う論理回路を実現している。最先端のCPUなどには、実に数十億ものトランジスタが集積されている。

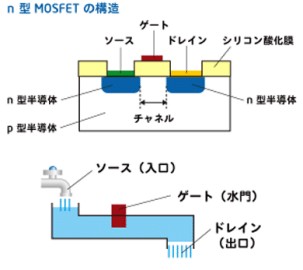

マイクロプロセッサーなどの集積回路には、一般的に、MOSFET (Metal Oxide Semiconductor Field Effect Transistor:金属酸化膜半導体電界効果トランジスタ) と呼ばれるトランジスターが用いられている。MOSFET は、外部から電圧を加えることで電流の流れを制御するトランジスターのことだ。構造が単純で集積させやすく、小さな電力で動作することが利点だ。MOSFET には、電流の入口となるソース、出口となるドレイン、電流の流れを制御するゲートという 3つの金属電極がある。そして、ゲートにかける電圧を制御することで、ソースとドレイン間の電流を流したり、止めたりしているのだ。

MOSFET では、ソースとドレインに同じ性質を持つ半導体を、そしてゲートの真下にあるチャネル領域にはその反対の性質を持つ半導体を配置する。例えば、n型と呼ばれる MOSFET は、ソースとドレインに自由電子を多く含む半導体 (n型半導体) 、そしてゲート下のチャネル領域には自由電子が不足している半導体 (p型半導体) を組み合わせている。逆に、ソースとドレインに p型半導体、ゲートに n型半導体を配置した p型の MOSFET もあり、これらの二種類の半導体を組み合わせたものを CMOS (Complementary MOS) と呼ぶ。

ゲートの役割は、庭のホースを足で踏んで水を出したり止めたりするようなもので、データのビットを構成する0と1を表現するために使用される。しかし、ゲートはホースと同じで不完全なものであり、どんなに高度に設計されたものでも、一部の電気がすり抜けてしまうことがある。これをゲートリーク電流というが、素子や配線の製造時の欠陥に起因する物ではなく、量子トンネル効果によるものだ。これは原子レベルの微細な世界において確率的に生じるもので、加工の微細化によって配線などの導体同士が近づくほど(間を隔てる絶縁体が薄くなるほど)急激に大きくなる。リーク電流の増大は、回路の誤作動の原因となるほか、本来の回路の動作に関係のない部分で電力が消費されてしまうことになる。そのため、発熱も増大し、熱暴走や回路の劣化や破損の原因となることもある。リーク電流をおさえることは、省電力性能・パフォーマンスのためにも大きな課題となるのだ。

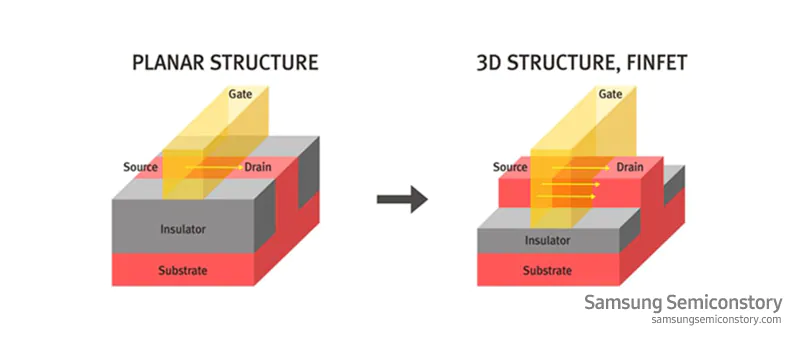

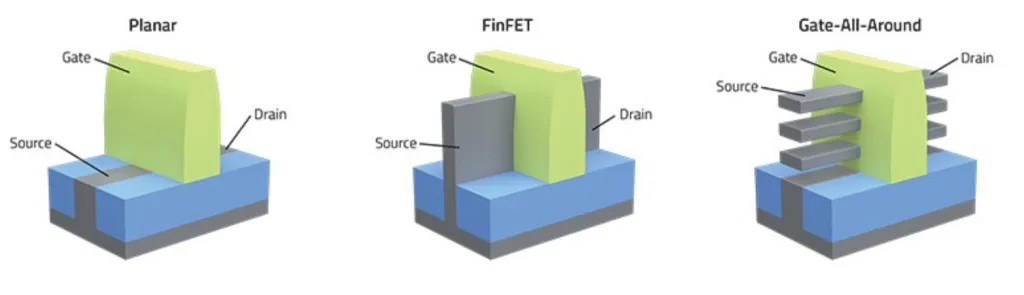

これを解決するために、現在の最先端半導体プロセスにおいて用いられているトランジスタは「FinFET」と呼ばれる立体構造をしている。これは先述した「MOSFET」の一種で、ゲートがチャネルの側面と上面の3面を取り囲むように3次元的な構造をしていることから、3次元トライゲートとも言われる。FinFETのFinは、その構造が、魚のひれ(Fin)に似ていることから名付けられた。

FinFETは2011年にIntelが世界に先駆けて22 nm世代のマイクロプロセッサーで取り入れた。それ以降、10年に渡って先端半導体のトランジスタとして採用されてきたが、5nm世代の半導体が量産されるようになってきた2022年では、FinFETでも微細化の限界が見えてきた。ゲートの薄型化、小型化が限界に近付くにつれ、リーク電流の増大が問題になってきたのだ。

FinFETの次を担うGAA FET

FinFETの限界を打破するために期待されているのが、現在のチャネルを3方向で囲むのではなく、4面全てをゲートで囲むことで、リーク電流を抑える方法だ。このチャネルを全て包み込む形から、「Gate All Around(GAA)FET:全周ゲートFET」と呼ばれている。

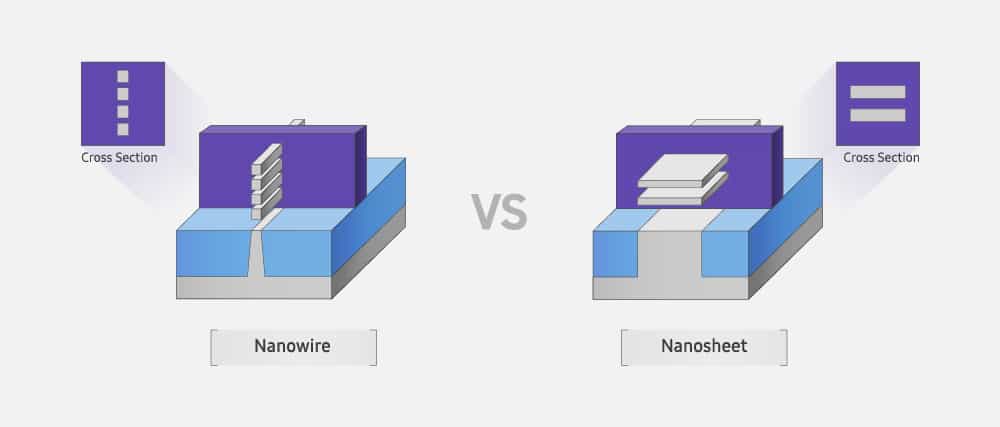

GAA FETでは細いチューブを縦に並べたような「Nanowire(ナノワイヤ)」や、細長いシートと重ねたような「Nanosheet(ナノシート)」が研究されていた。

Nanowireはチャネルが細く小さいため、流せる電流が少なくなることなどから、現在はNanosheet構造を次世代ノードでは各社取り入れるようだ。

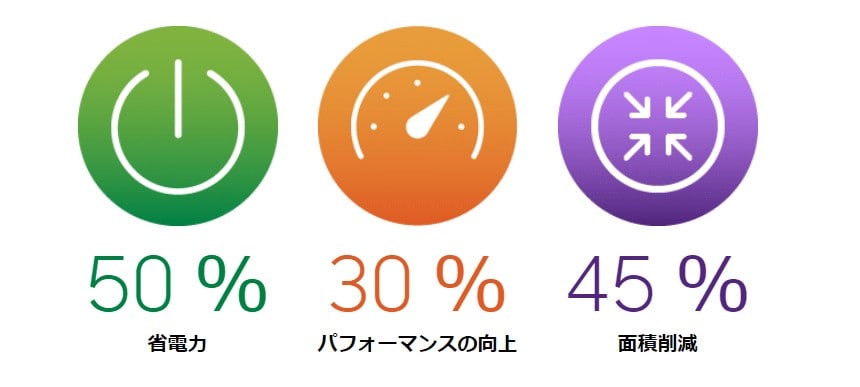

3nm世代でのGAA FETはSamsungが他社に先駆けて量産を開始することが報道されている。同社はNanosheet方式の「MBCFET(Multi Bridge Channel FET)」と名付けたプロセスでTSMCからシェアを奪還したい考えだ。

同社によると、MBCFETの導入により、「50%の省電力、30%のパフォーマンスアップ、45%の面積削減」が期待できるとのこと。

Samsungは先行してGAA FETの量産を開始しているが、歩留まりが低くまだ軌道には乗っていないようだ。これをいかに安定して供給できるかに今後の同社の命運がかかっているだろう。

TSMCは3nm世代ではまだFinFETを採用するようだが、その先の2nm世代からNanosheetベースのGAA FETを採用する事を先日発表している。

新世代のゲート技術を大量生産することに成功したメーカーは、現在のプロセス技術では不可能な、演算能力が飛躍的に向上したチップを製造することができるようになり、市場で優位に立てるだろう。

現在首位となっているTSMCも今後の他社の動向によってはこの勢力図が塗り替えられることもありそうだ。

コメントを残す