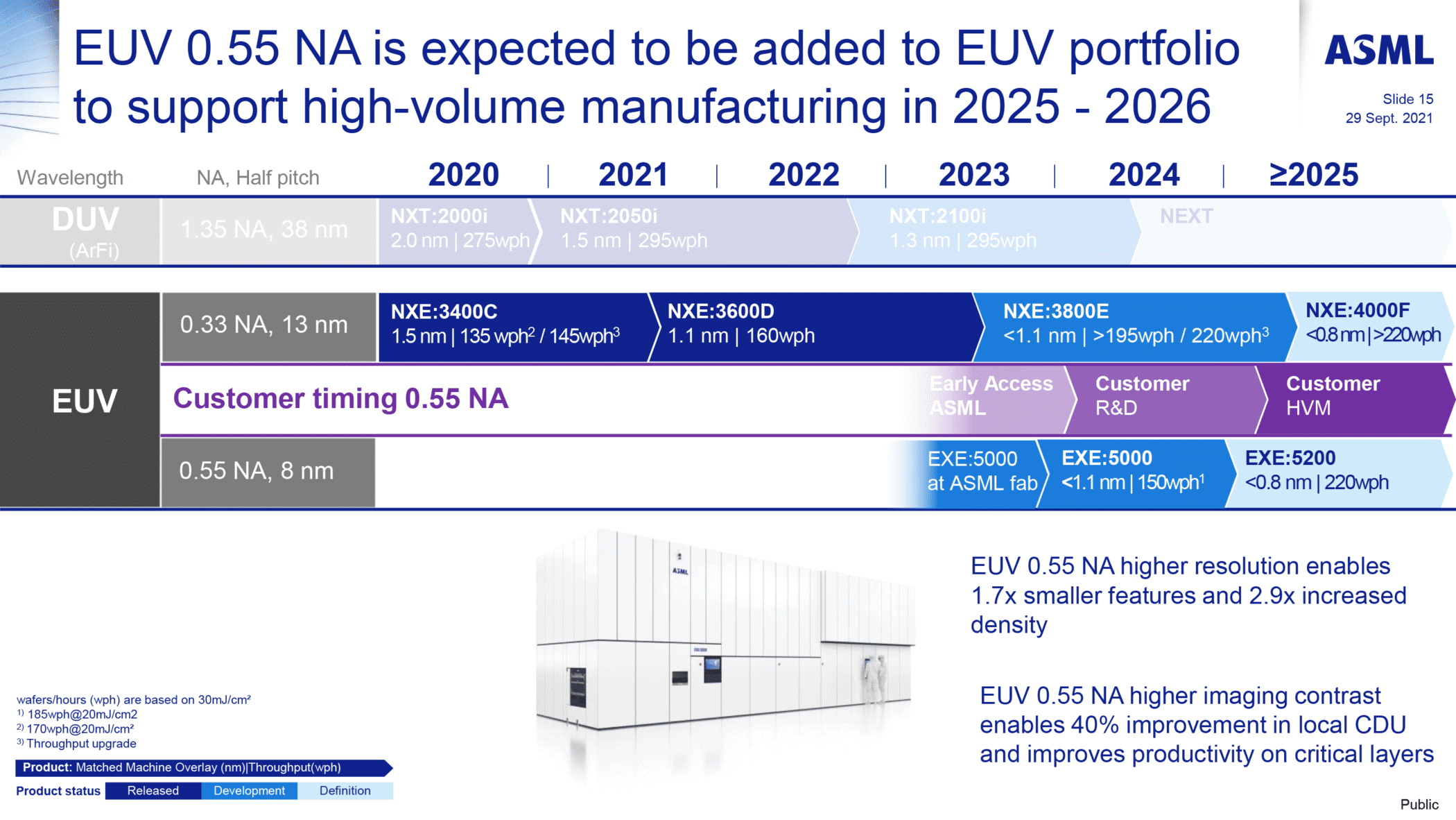

半導体製造装置の世界では、オランダのASMLだけが、最先端のチップ開発が可能となる装置の製造を行っている。ASMLは、ファウンダリーが時間とともにより小さなノードに切り替えていくのと同様に、TSMCやインテルなどの企業が最先端を維持するために購入する必要がある、より高度な技術を搭載した新しいマシンも製造している。最も先端的な装置は、高開口数(High-NA)EUVリソグラフィ装置であり、Intelはすでにこれを導入した。TSMCもこれに続くと見られるが、新たな報告によると、TSMCは1nmプロセスの登場まで待つ予定であり、それは2030年頃になると予想されている。

TSMCの計画に関する報道はさまざまな情報源から寄せられているが、最新のものはDigiTimesである。同誌に、「ファブ・ツールメーカー」の情報筋からもたらされた新たな情報によると、TSMCは2025年と2027年前後に登場する予定の2nmと1.4nmノードではHigh-NAマシンを使用しない見込みだという。その代わりに、TSMCは今からおよそ6年後に登場する可能性のある1nmまで待つことになり、最新のチップ製造技術を採用する際にライバルから数年遅れることになる。

Tom’s Hardwareによれば、これはコストに起因するかもしれないとのことだ。これらのマシンは途方もなく高価で、『WarGames』のWOPRのようなルームサイズのコンピューターに似ているため、その購入と設置は大変な作業となる。以前はアナリストも、High-NAマシンの採用は、既存のLow-NAマシンの2倍、1台あたり3億ドルとも4億ドルとも言われるコストを考えると、財務的な意味はほとんどないと述べていたが、ASMLはこの主張を全面的に否定している。Tom’s Hardwareによると、ASMLの幹部は、アナリストがHigh-NAマシンへの切り替えのメリットを過小評価していると非難した。

この議論の核心は、1回の露光でマスクを作る利点と複数回の露光でマスクを作る利点をめぐる問題に帰着する。Low-NAマシンは複数回の露光が必要で、欠陥が発生する可能性が高くなり、歩留まりも低下する。High-NAマシンでは1パスで露光できるため、複雑さが軽減され、エラーが発生する可能性が低くなるとともに、製造工程の時間も節約できる。Tom’s Hardwareが指摘するように、既存の13nmマシンは、High-NAの8nmマシンが1パスでできるのと同じマスクを2パスで作ることができる。つまり、最先端にとどまるために今すぐアップグレードすることは、必ずしも必要ではなく、TSMCのような企業がしばらく待つことを望む理由である。

この技術の採用には無数の要因が絡んでいるが、2022年にIntelとASMLはHigh-NAマシンで提携すると発表した。Intelは、1.4nmプロセスであろうインテル18A以降のノードでこのマシンの使用を開始すると予想されているが、Intelはまだ公式には明らかにしていない。しかし、同社は2月21日にファウンドリー・イベントを開催し、そこでプロセス・ロードマップを拡大すると予想されているため、インテルがどこに向かっているのかはまもなく判明するだろう。

また、Samsungは独自にASMLと半導体研究で提携を進めており、更にHigh-NAマシンの優先購入権を確保したと報じられている。

Sources

コメントを残す