TSMCが、まもなくN3(3nmクラス)製造プロセスによる生産を開始すると、新竹で開催された年次技術フォーラムで明らかにしたとNikkei Asiaが報じている。同社はN3プロセスを最初に使用する予定の顧客を明らかにはしていないが、非公式な情報によると、AppleがTSMCの最先端ノードの最初の顧客になるようだ。

以前より、非公式の情報筋はTSMCが9月にN3製造ノードでのチップ生産を開始する意向だと示唆していたが、同社がまだ最先端ノードでの製品製造を開始していないこと、3nmチップの量産(HVM)を「まもなく」開始する予定であることを確認したのはこれが初めてである。

2020年にHVMに入ったTSMCのN5プロセスと比較すると、ファウンドリの第1世代N3プロセスは、10%~15%の性能向上(同じ電力と複雑さの場合)、25%~30%の消費電力削減(同じ速度とトランジスタ数の場合)、そして約1.6倍のロジック密度の向上を約束している。

| N3E vs N5 | N3 vs N5 | |

|---|---|---|

| 速度向上率(同じ電力の場合) | +18% | +10% ~ 15% |

| 電力削減率(同じ速度の場合) | -34% | -25% ~ -30% |

| ロジック密度 | 1.7倍 | 1.6倍 |

| HVMスタート | 2023 年第 2 四半期/第 3 四半期 | 2022 年下半期 |

N3にはその後にも改良版のノードが複数用意されており、順次追加される予定だ。N3Eはプロセスウィンドウの改善、N3Pは性能の向上、N3Sはトランジスタ密度の向上、N3XはCPUなどのアプリケーション向けにさらなる性能最適化を実現するとのことだ。3nmファミリーのノードは今後何年にもわたって使用されることになる。

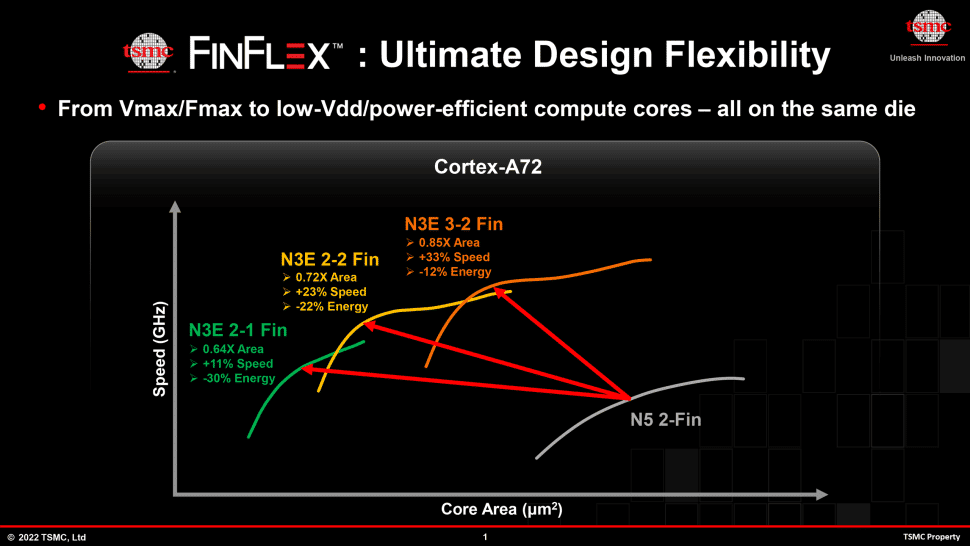

N3の主な特徴の1つは、ファブレスチップ開発者の設計柔軟性を大幅に向上させたTSMCのFinFlexテクノロジーだ。この技術により、設計者は1つのブロック内で異なる種類のスタンダードセルを混在させ、性能、消費電力、面積を正確に最適化できるようになり、高トランジスタ密度と高クロックを両立しなければならないCPUやGPUコアなどの複雑なデバイスに特に有利になる。その結果、Apple、AMD、Intel、MediaTek、NVIDIAなど、複雑なシステムオンチップを構築する企業は、FinFlexの恩恵を受けることができる。

TSMCの最大の顧客であるAppleは、このファウンドリのN3技術を採用する最初の企業となる見込みだが、同社がこのノードを使用して具体的に何を生産する計画なのかは不明である。その後、この技術はIntelのほか、AMD、NVIDIA、MediaTek、Qualcommなど、TSMCの他の顧客企業にも採用される予定だ。

Source

コメントを残す