Intelが、自社製品やIntel Foundry Services(IFS)部門の顧客向けチップの製造に使用されるIntel 18A(1.8nmクラス)およびIntel 20A(2nmクラス)の製造プロセスの開発を完了したと報じられている。

Intel Chinaの社長兼会長であるWang Rui氏は、同社がIntel 18A(18オングストローム級)およびIntel 20A(20オングストローム級)の製造プロセスの開発を最終決定したことをイベントで発表した。とはいえこの開発完了は、製造ノードが商用製造に使えるようになったという意味ではなく、Intelが両技術の仕様、材料、要件、性能目標をすべて決定したことを意味するものだ。

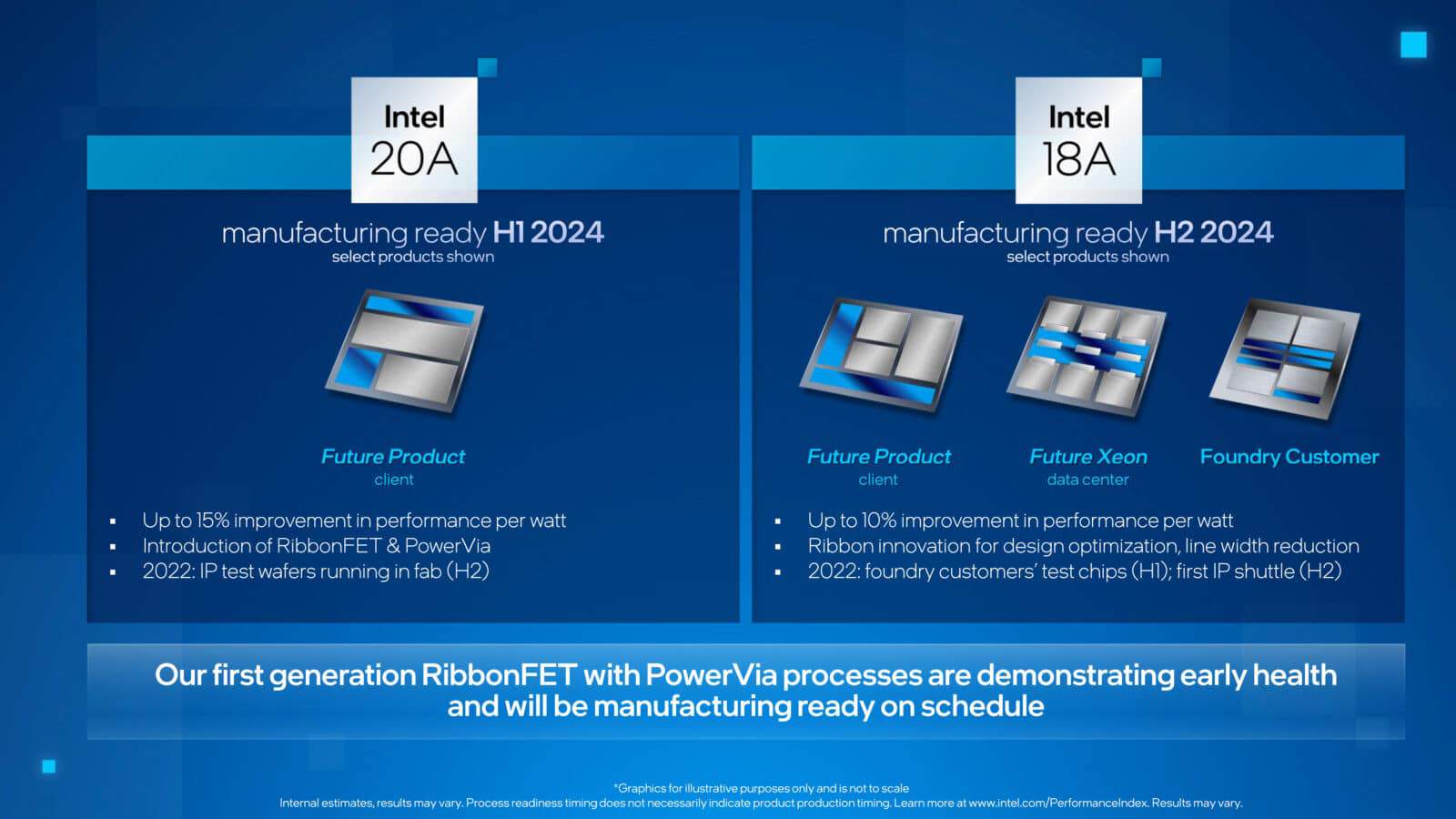

Intelの20A製造プロセスは、Gate All Around(GAA)のRibbonFETトランジスタと、バックサイドパワーデリバリー(BPD)であるPowerViaを使用する予定である。金属ピッチを縮小し、全く新しいトランジスタ構造を導入した上で、同時に裏面給電まで追加することはかなり挑戦的なことではあるが、これによりIntelは競合他社であるTSMCやSamsung Foundryを追い抜き、かつての栄光を取り戻すことができると予想される。Intelは、2024年前半にこのノードの使用を開始する予定だ。

Intelの18A製造プロセスは、同社のRibbonFETとPowerVia技術をさらに洗練させ、トランジスタのサイズを縮小させる。このノードの開発は、Intelがその導入を2025年から2024年後半に前倒しにしているほど順調なようだ。Intelは当初、1.8オングストローム・ノードにASMLのHigh NAである0.55開口数(NA)光学系のTwinscan EXEスキャナーを使用する予定だったが、この技術の使用を早期に開始することにしたため、0.33NA光学系の既存のTwincan NXEスキャナーとEUVダブルパターニングを幅広く使用しなければならないことになる。

同社自身も、1.8nmクラスの製造技術が2024年後半にHVM(High Volume Manufacturing:大量生産)に入る際には、業界最先端のノードになると予想している。

Intelの20Aおよび18A製造技術は、自社製品だけでなく、IFSがファウンドリー顧客向けに製造するチップ向けにも開発されている。

Intelの最高経営責任者であるPat Gelsinger氏は、アナリストや投資家との最近の電話会議で、「我々は、10大ファウンドリ顧客のうち7社と積極的に契約し、43の潜在顧客とエコシステムパートナーのテストチップを含む一貫したパイプラインの成長を続けている」と述べた。”さらに、我々はIntel 18Aの進捗を続けており、すでにPDK 0.5(プロセスデザインキット)のエンジニアリングリリースをリード顧客と共有しており、今後数週間で最終的な生産リリースを行う予定です」と、述べていた。

Source

- UDN: 英特爾強碰台積電 傳2奈米研發突破

コメントを残す