eeNewsによると、今年の12月にサンフランシスコで開催される、国際電子デバイス会議(IEDM)において、IntelとTSMCは、垂直積層型相補型電界効果トランジスタ(CFET)の進捗状況を発表する予定のようだ。

CFETは、ゲートオールアラウンド(GAA)マルチチャネルトランジスタの次に来るとされるトランジスタのアーキテクチャである。GAAは、3nmと2nmのノードでTSMC、Samsung、Intelなどの半導体製造メーカーによって、先端ノードで採用される(または採用される予定)である。

CFETの概念は、n型とp型のトランジスタが垂直に積層される形で、2018年にIMECの研究機関によって提案された。それ以降、多くの研究論文がこの提案について詳しく研究されているが、初期の研究は主にIMECや学術研究者によるものであった。ここ数年、商業組織のR&Dチームもこの分野に進出し、次世代トランジスタの有望株として研究を続けている。

Intel

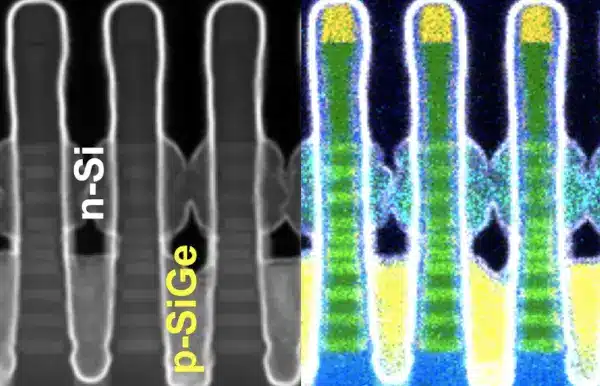

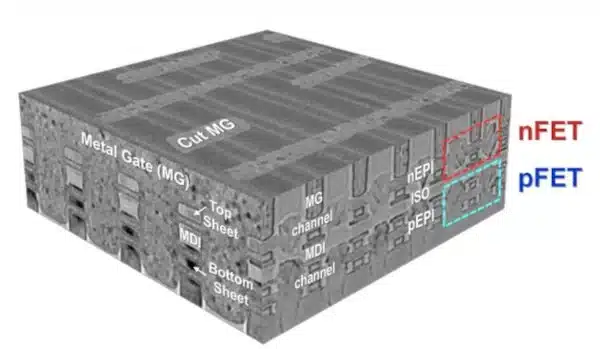

IEDM会議で、Intelの研究者は、3つのn-FETナノリボンと3つのp-FETナノリボンから成る3DモノリシックCFETデバイスについて発表する予定だ。このデバイスは、垂直方向に30nmの間隔を持つ。

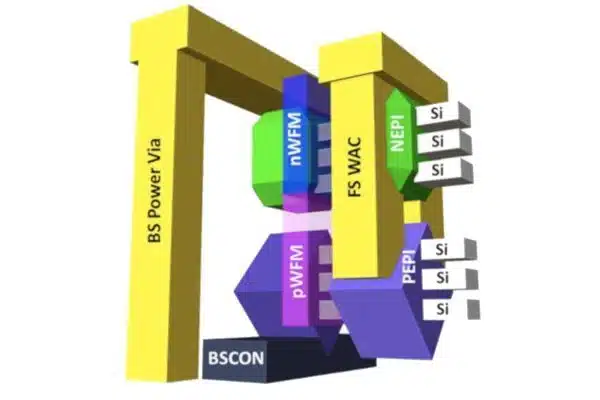

Intelは「Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts」と題する発表で、60nmゲートピッチのCFETを利用した機能的なインバータテスト回路について説明する予定だ。この設計はまた、ソース・ドレイン二重エピタキシーとツイン・メタル・ゲート・スタックを垂直に積層し、同社のPowerViaバックサイド・パワー・デリバリーを組み込んでいる。

TSMC

TSMCの研究者も、48nmのゲートピッチでのロジック技術のスケーリングに対する実用的なモノリシックCFETアプローチについて議論する予定である。この設計は、n型のナノシートトランジスタがp型のナノシートトランジスタの上に積層されており、非常に優れたオン/オフ電流比を実現するという。TSMCのトランジスタは、90%以上がテストに成功しており、CFET技術の可能性を最大限に引き出すためにはさらなる特長が組み込まれる必要があると認めつつも、この作業はその目標に向けた重要なステップであるとされている。

CFETは、GAA、FinFET、または平面アーキテクチャで一つのトランジスタが占めるスペースに二つのトランジスタを配置できるという明らかな利点を提供する。これにより、CMOSロジック回路をより効率的に設計できる。特に、トランジスタ端子へのアクセスが主に標準セルエリアに依存するという点で、CFETはこれを簡素化できるとIMECは以前に指摘している。

さらに、CFET固有の構造により寄生効果が低減され、性能と電力効率が向上する可能性がある。NMOSとPMOSのチャネル・バリエーションをバランスさせる能力など、CFETの順応性の高い設計能力は、バックサイド・パワー・デリバリーなどの技術革新と相まって、製造プロセスをさらに合理化し、CFETをトランジスタ技術の領域における有望な次の技術と位置づけている。

Source

コメントを残す