AMDの次世代EPYCシリーズは、Zen6アーキテクチャを搭載し、最大64コアの「Venice」Zen6コアとPCIe Gen6サポートを特徴とすることが、Moore’s Law is Dead(MLD)の報告により明らかになった。AMDのZen6アーキテクチャは、消費者市場やデータセンターにはまだ提供される予定がない。同社は、Zen5アーキテクチャを全市場セグメントにリリースする前の段階にあり、一部のZen4製品(Hawk Point、MI300など)の発表が続いている。AMDには長期的なロードマップがあり、先進的な計画が異なる市場での足場を築く鍵となっている。

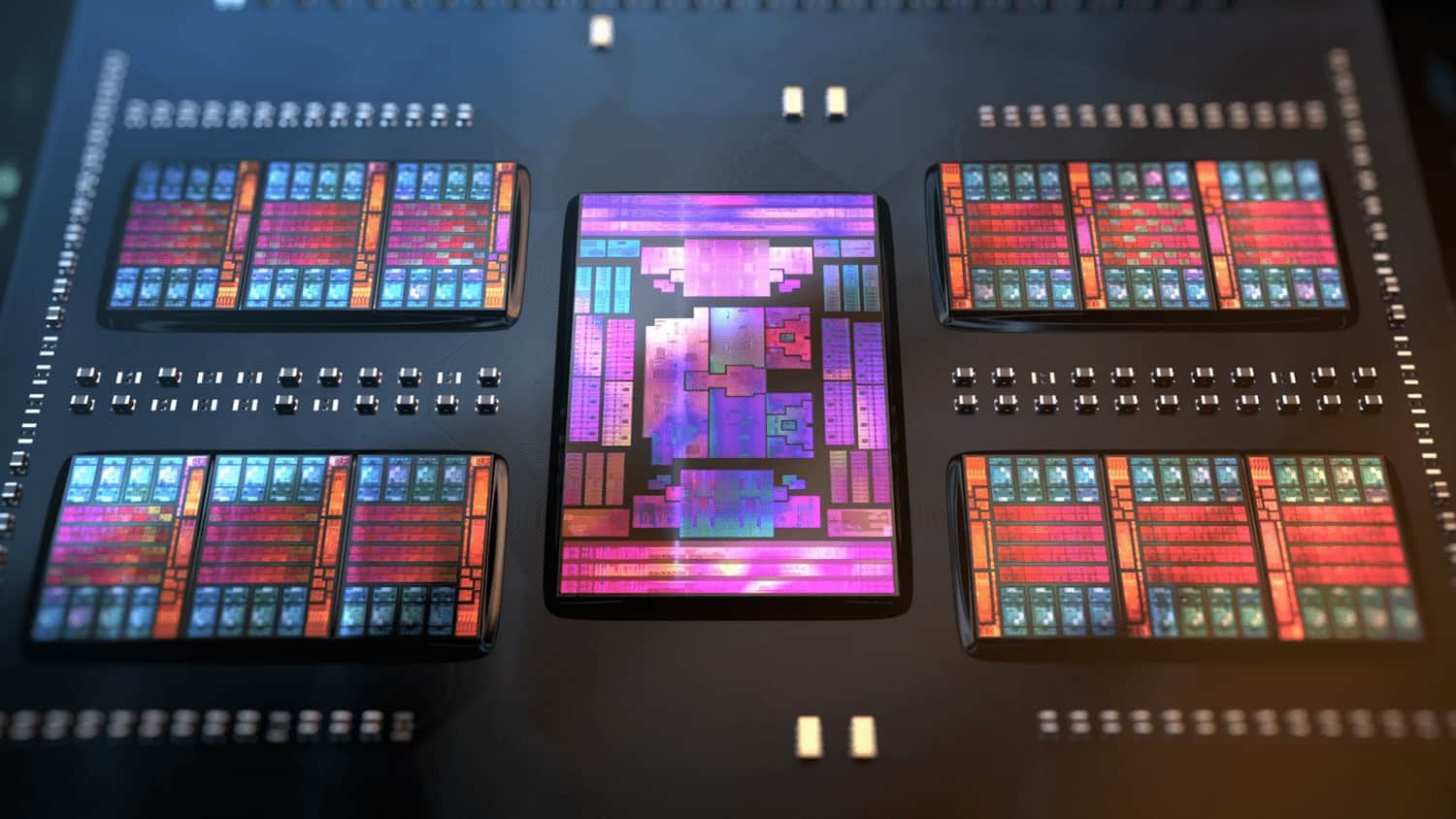

Zenの革命は、新しいレイアウトデザインと新しいパッケージング技術を備えた第6世代に到達しようとしており、Zen5からの大幅な再設計になるとリーカーは主張している。EPYCシリーズでは、AMDはCPUコア、ネットワークIP、カスタムFPGAを組み込んだチップレットを組み合わせている。このアプローチは、さまざまな新しい可能性を開き、従来のCPUと目的特化型アクセラレーターとの区別を徐々に曖昧にしている。

9月頃、MLIDはAMDの内部スライドデッキから直接Zen5とZen6の最初のアーキテクチャの詳細を共有した。これにより、両アーキテクチャのコードネームがNirvanaとMorpheusであることが確認された。ビデオは主にZen5に焦点を当てていたが、Zen6に関する詳細は、AMDがチップレットあたりのコア数(最大32)の増加と、AIおよび機械学習用の高精度浮動小数点(FP16)演算の加速を目指していることを確認した。

MLIDは現在、EPYC-E製品シリーズの図を公開しており、EはEdge(エッジ)を意味すると思われる。これは、コア数が少なく、消費電力が低い通信およびエッジシステム用に設計されたものである。図に示されている製品は、Venice SP8 IODと、それぞれの側に2つのCCDを備えたもので、32のZen6コアを特徴としている。この特別なCPU設計では、CCDのいくつかをPensando Salina設計に基づくNCD(Network Compute Die)に置き換えることも可能である。

比較的に、このEPYC-E設計に使用されるSP8ソケットは、EPYCシリーズの一部に対して次のCPUソケットになるだろう。これは、より大きなVenice CPUをホストするSP7と同時に発売される予定である。SP8は、Siena & Soranoの後継として計画されている小型ソケットである。

EPYC-Eは、64のZen6コアを備えた「スタンダード」エディションと、32コアの「エントリー」バリアントの2つのバリアントで登場する予定である。スタンダードエディションには、オクタチャンネルDDR5-6400メモリサポートと64のPCIe Gen5および32のPCIe Gen6インターフェースサポートが備わっている。エントリーEPYC-C CPUには、同じ速度のクアッドチャンネルメモリサポートと32(Gen5)および16(Gen6)のPCIeレーンが備わっている。

1つのCCDが32コアを提供し、エントリーEPYC-Eシリーズがそのようなコア数に制限されていることから、AMDはCCDの1つをNCDタイルに置き換える可能性があることを示している。同様に、スタンダードエディションでは、2つのZen6チップレットがカスタムFGPAおよびNCDに置き換えられる可能性がある。

MLIDは、新しいドキュメントへのアクセスといくつかの教育的な推測に基づいて、SP7ソケット用の可能なZen6 EPYCプロセッサのモックアップを作成した。AMDは現在、Zen6と仮定されるZen6c(クラウド/密集)コアとの区別を行っていないが、これはAMDがこの区別から離れているか、そのようなコアが計画されていないためかもしれない。いずれにせよ、4つのIODダイを備えた可能な8チップレット設計は、現在の96 Zen4(Genoa)または128 Zen4c(Bergamo)設計、および将来のTuringの128/192 Zen5(クラシック)またはZen5(Dense)コアからのコア数を最大256まで増加させる可能性がある。

Source

コメントを残す