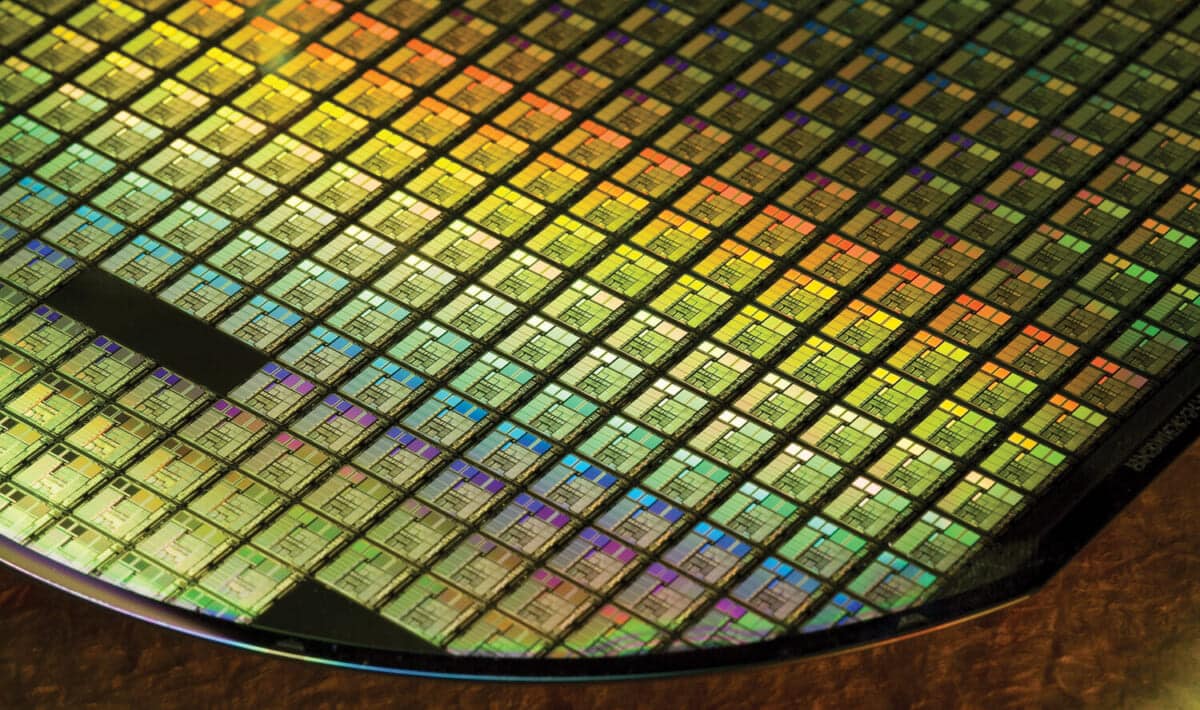

TSMCは、ヨーロッパで開催された年次のOpen Innovation Platform(OIP)フォーラムの一環で次世代の半導体製造技術に関する進捗を発表した。同社は、2nmクラスのN2、N2P、N2Xプロセス技術を導入する予定であり、これにはナノシートのゲートオールアラウンド(GAA)トランジスタ、裏面電源供給ネットワーク(BS-PDN)、超高性能の金属-絶縁体-金属(SHPMIM)キャパシタなど、多くの革新的な技術が含まれる。

TSMCによれば、これらの新技術を活用するためには、チップ設計者は全く新しい電子設計自動化(EDA)ツール、シミュレーションツール、検証ツール、およびIPを使用する必要がある。幸いなことに、N2の導入がまだ数年先であるにもかかわらず、主要なEDAツールや検証ツール、基本IP、さらにはアナログIPの多くがすでに使用可能であるという。

TSMCの設計インフラストラクチャ管理部門の責任者であるDan Kochpatcharin氏によれば、ナノシート技術は従来のFinFETとは異なるため、EDAツールやその他のツール、IPメーカーは製品を一から開発する必要があった。これに対応するため、TSMCのオープン・イノベーション・プラットフォーム(OIP)がその実力を発揮し、TSMCのパートナー各社が製品の開発をかなり前から開始できるようになった。

現在までに、CadenceやSynopsysの主要なEDAツール、Ansys やSiemens EDAの多くのツールがTSMCの認定を受けており、チップ開発者はすでにこれらのツールを使ってチップを設計できる。また、CadenceやSynopsysのEDAソフトウェア・プログラムは、アナログ設計の移行に対応している。さらに、CadenceのEDAツールはすでにN2Pのバックサイド・パワー・デリバリー・ネットワークをサポートしている。

「ナノシートトランジスタを搭載したIPの開発は)難しいわけではありませんが、サイクルタイムが長くなります。これらのIPベンダーの中には、トレーニングが必要なところもあります。プレーナー(トランジスタ)からFinFETに移行するのは難しくありません。[同じことです。ですから、訓練は必要ですが、(訓練すれば)簡単です。だから私たちは早くから始めたのです」と、Kochpatcharin氏は説明する。

2025年下半期に予定されているN2チップの量産開始に向けて、多くの準備が進行中である。大手企業はすでに2nmチップの設計に取り組んでおり、量産が始まる頃には製品が完成する予定である。

Source

コメントを残す