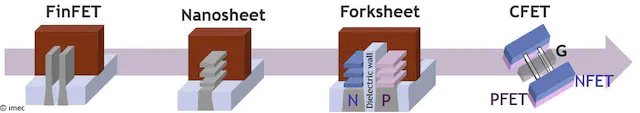

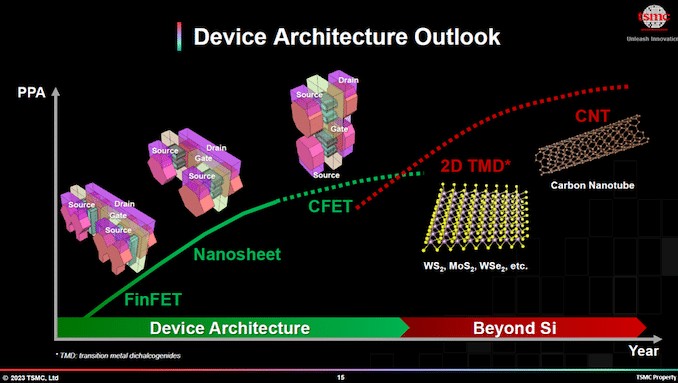

TSMC は、European Technology Symposium 2023 において、次世代のシリコンベースのデバイスを駆動する相補型FET (CFET) 技術に関する追加事項を発表した。FinFETからGAAFET(ナノシート)に代わる中、CFET技術は将来的にそのGAAFETを置き換える物になる。

同社が述べているように、CFETは現在TSMCのラボで、性能、効率、密度のテストが行われている。GAAFETと比較して、CFETはこれらすべての領域でより優れた設計を提供するが、チップを意図通りに動作させるためには、いくつかの製造工程を追加する必要がある。p型とn型の両方のFETを1つのデバイスに統合したCFETを製造するには、高精度と高出力を備えたHigh NA EUVスキャナーの使用が必要になるのだ。

ロードマップが示すように、CFETの使用はシリコン半導体における最後のステップの一つである。その後は製造プロセスに新材料を組み込む必要があり、その結果、ノード創出を担当する研究開発への投資も大きくなる。TSMCのシニアバイスプレジデントで、技術ロードマップとビジネス開発を担当するKevin Zhang氏は、こう指摘する:「ナノシートの先にあるものは、まだ未来があることを伝えるために、我々の(ロードマップに)載せるものです。私たちは、今後もさまざまな選択肢に取り組んでいくつもりです。また、一次元材料ベースのトランジスタについても、現在、将来の候補として研究中であり、ナノシートを超えるトランジスタのアーキテクチャを正確にお伝えすることはできません」。

ラボレベルでのCFETの駆動は以前から他の研究者も行っているため、驚くべき事ではないが、TSMCはその先の、量産を実現する方法を考えなければならない。そのため、TSMCは、CFETが近い将来に登場するわけではないことを強調している。

CFETに取り組んでいるといっても、研究が進めば新しい技術が生まれるかもしれない。ただ、現在「決まっている」のは、2nmノードでスタートするナノシートGAAGET技術だけである。さらに、Zhang氏は「このナノシートが2nmから始まるということは、予想するのが妥当で、そのナノシートは少なくとも数世代は使われることになりますよね?CFETについて考えてみると、我々は5世代にわたって[FinFET]を活用してきたわけで、10年以上になる。多分、[デバイス構造]は心配するのは他人事で、それなら物語を書き続けることができま」と、述べている。

Source

コメントを残す