2022年の技術シンポジウムで、TSMCはN2(2nmクラス)製造技術を正式に発表した。この技術は2025年のに生産開始される予定で、TSMCのナノシート・ベースのゲート・アラウンド電界効果トランジスタ(GAA FET)を使用した最初のノードとなる。

Toms’s Hardware : TSMC Reveals 2nm Node: 30% More Performance by 2025

この新しいノードによって、チップ設計者は製品の消費電力を大幅に削減することができるが、速度とトランジスタ密度の向上は少し微妙なところだ。

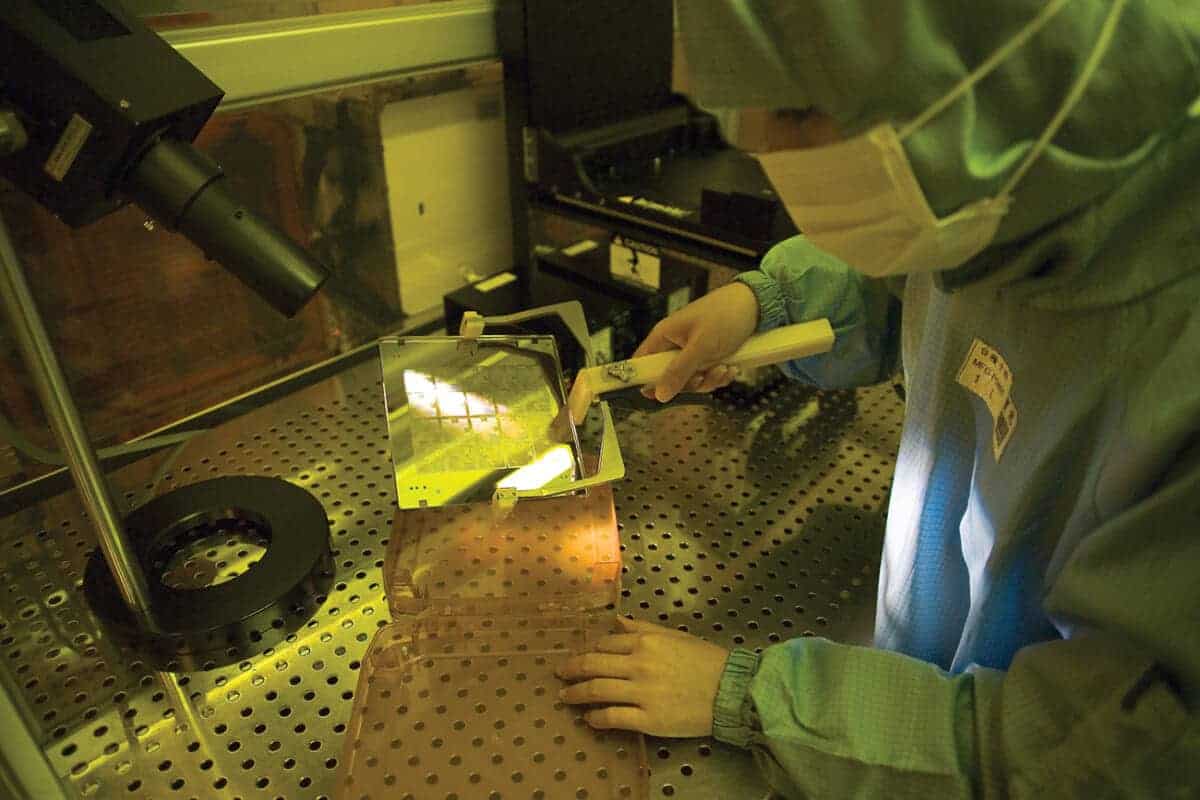

TSMCのN2は、EUVリソグラフィを多用し、GAA FET(TSMCはナノシートベースの全周ゲートFET)と裏面給電を導入した全く新しいプラットフォームである。GAA(Gate All Around)構造では、チャネルの4辺にゲートがあるためリーク電流が大幅に減少し、チャネル幅を調整することで性能向上や消費電力低減が可能になるなどの利点が知られている。裏面パワーレールについては、一般にトランジスタへの電力供給を改善するために設計されており、BEOL(Back End of Line)の抵抗増加の問題に対する解決策を提供するものである。この新しい電力供給により、トランジスタの性能向上と消費電力の低減が期待される。

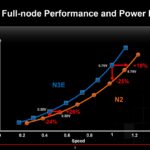

機能セットという観点からは、TSMC の N2 は非常に有望に見える。実際の数値について、TSMCは、N2によって、同じ電力とトランジスタ数で、従来よりも性能を10%~15%向上させる事が出来るか、もしくは同じ周波数と複雑さで消費電力を25%~30%削減させられ、N3Eノードと比較してチップ密度を1.1倍以上向上させられるとしている。

| N5 vs N7 | N3 vs N5 | N3E vs N5 | N2 vs N3E | |

|---|---|---|---|---|

| 消費電力 | -30% | -25-30% | -34% | -25-30% |

| パフォーマンス | +15% | +10-15% | +18% | +10-15% |

| チップ密度 | ? | ? | ~1.3X | >1.1X |

| 大量生産開始時期 | Q2 2022 | H2 2022 | Q2/Q3 2023 | H2 2025 |

だが、N3E と比較すると、TSMC の N2 ノードが実現した性能向上と電力削減は、ファウンドリの新ノードが通常もたらすものと同レベルのものだ。これはGAA FETに移行する物としては控えめな印象を受ける。いわゆるチップ密度の向上(トランジスタ密度の向上を反映するはず)は10%強で、特にN3Eが標準N3と比較してすでに若干低いトランジスタ密度を提供していることを考えると、これは特に驚くことではない。SRAMやアナログ回路がほとんどスケールしない昨今、実際のチップのトランジスタ密度の向上は、平凡なものであると考えるべきだろう。しかし、3年程度で10%程度のチップ密度の向上は、GPUなどトランジスタ数の急増が生きるか死ぬかのチップにとっては、決して良いニュースではないだろう。

TSMCのN2が生産に入る頃には、同社は密度を最適化したN3Sノードも持っていることを考えると、ファウンドリは、異なる種類のトランジスタをベースにしながら、非常に似たトランジスタ密度を提供する2つのプロセス技術を持つことになり、これは過去に一度もなかったことである。

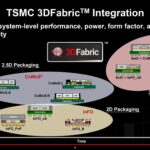

通常通り、TSMCはN2ノードを提供し、チップ設計者がモバイルやハイパフォーマンスコンピューティング設計などに最適化できるように、さまざまな機能や付加価値を提供する(TSMCは、モバイル、自動車、特殊用途以外のものをすべてHPCと呼んでいることに注意したい。)また、プラットフォームの提供には、TSMCが「チップレット統合」と呼ぶものが含まれる。これはおそらく、TSMCの顧客が、さまざまなノードを用いて製造したマルチチップレットパッケージに、N2チップを容易に統合できるようにすることを意味している。トランジスタの集積度は鈍化し、新しいプロセス技術はより高価になるため、開発者は設計とコストを最適化するためにマルチチップレットパッケージを使用するようになり、今後数年間でより一般的になっていくだろう。

TSMCは、N2製造プロセスを用いたチップのリスク生産を2024年後半に開始する予定であり、この技術は2025年後半に商用製品の大量生産(HVM)に利用できるはずだ。しかし、現代の半導体の生産サイクルの長さを考慮すると、すべてが計画通りに進めば、最初のN2チップが利用可能になるのは2025年のかなり後半か2026年と予想する方がより現実的だろう。

コメントを残す