Samsungは、アメリカ カリフォルニア州で開催された Samsung Foundry Forum において、今後 5 年間でプロセス技術を 1.4nm に進めることを発表し、2027年には、ファウンドリ事業を2021年の3倍にまで成長させる計画であると発表した。

Samsungは、3nmファウンドリーウェハーの出荷を開始したことを発表し、3nm技術の量産化を他社に先駆けて実現していることを強調している。

フォーラムでは、Samsung Electronicsのファウンドリビジネス担当副社長であるMoon-soo Kang氏が、2027年までに1.4nm技術開発を達成するために、多くの半導体技術で飛躍的に進歩し、米国でのファウンドリビジネスを拡大させると述べた。

Samsungは、長期的な計画として、2027年までに1.4nm技術開発に参入する計画を発表したが、まずは、3nmプロセスの今後についての計画についてご紹介しよう。

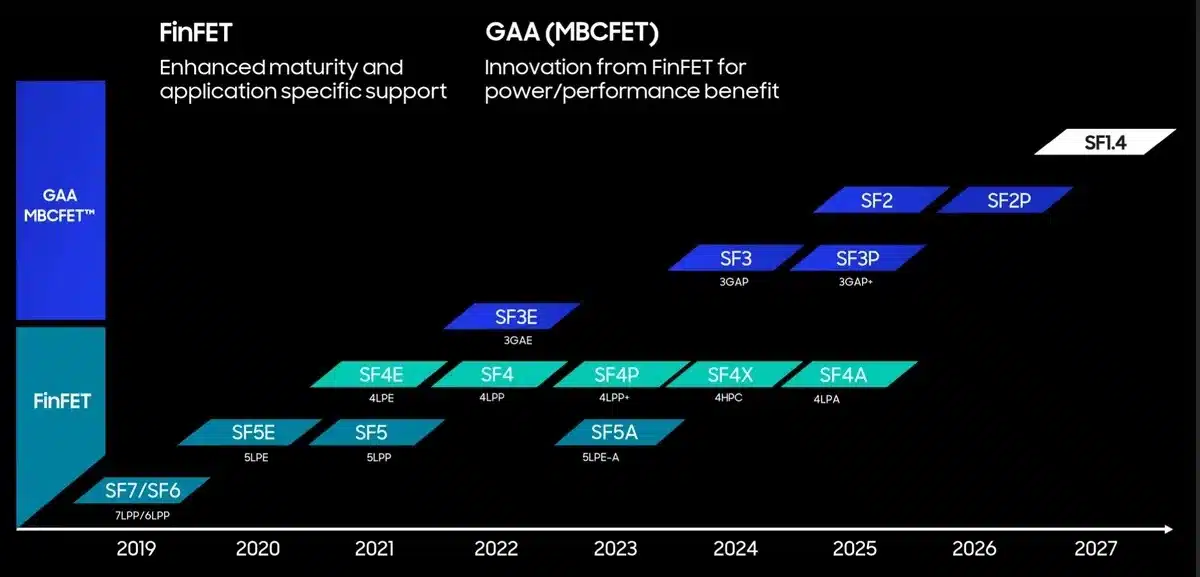

Samsung Foundryは、少し前に GAA (Gate All Around) テクノロジを搭載した世界初の 3nm チップ(SF3E) の大量生産を開始した。GAA はチップの基本構成要素であるトランジスタに対する大きな変革であり、数年に一度の大きな変化となる。同社は、この技術の助けを借りて、電力効率の大幅な改善を約束している。そして、Samsungは、2024 年までに第2世代の 3nm 半導体チップ (SF3) を導入する予定だ。

第2世代の 3nmチップは、第1世代の3nmチップよりも 20%小さいトランジスタを搭載すると述べている。これにより、スマートフォン、PC、クラウド サーバー、ウェアラブル向けの小型で電力効率の高いチップが実現する。

Samsung は、SF3P+ プロセスを使用して 3nm トランジスタ製造技術をさらに強化し、2025 年までに大量生産を開始する予定だ。同社は、GAA チップを大量生産できることをすでに証明しており、第2世代および第3世代のGAAチップは、いくつかの大口顧客をの興味を引く可能性がある。既にQualcommが、TSMCに加えて、Samsungとの接触も図っているようだ。

また、Samsungは、2025年までに2nm技術を量産化することを明らかにし、それによってウェハーの量産能力を高めるとしている。あわせて、裏面電力供給も採用する予定だ。通常、トランジスタへの電力供給とトランジスタとの通信は、半導体チップの片側のみを介して行われているが、新しい裏面電力供給技術により、通信と電力供給がチップの両面に分割される。これにより、チップ全体のパフォーマンスが向上する。Intelも、2024 年までに同様の機能 (PowerVia) をチップに搭載する予定だ。

また、Samsung Foundry は、新たに1.4nm (SF1.4) という新しいノードを計画している事を発表した。同社は 2027 年までに 1.4nm チップの大量生産を開始する予定だ。このプロセスノードで期待される改善点についての詳細は明らかにされていないが、性能の向上はゆっくりではあるが着実にあるとしている。

同社はまた、2.5D/3D 異種統合パッケージング技術を改善している。Samsung のマイクロバンプ相互接続を備えた 3D パッケージング X-Cubeは 2024 年に、バンプレス 3D X-Cube は 2026 年に利用可能になる予定だ。Samsung はまた、2022 年に比べて 2027 年までにチップ生産能力を 3 倍に拡大することを計画している。

Samsungは、テキサス州オースティンの施設に加え、テキサス州タイラー近郊にも新施設の建設を計画しており、2024年の稼働を目指し、最新の3nm技術による量産に向けたファウンドリリソースを提供する予定だ。

また、Samsungは、チップ需要の50%を自動車、HPC(High-Performance Computing)、IoT、5Gの各市場から得られると見込んでいる。同社は強化された4nmプロセスを使って、車載とHPC分野向けのチップを製造する予定だ。現在、自動車顧客向けに28nmのeNVMチップを製造しているが、2024年には14nm eNVMソリューション、将来的には8nm eNVMソリューションでそれを改善する計画であるという。

さらに同社は現在、通信分野向けに8nmのRF(Radio Frequency)チップを製造しており、まもなく発売できる5nmのRFチップを開発しているところである。また、同社は半導体工場に「クリーンルーム」を計画している。これらの区画では、同社が工場設備を保管し、需要の増加に応じて後で使用することが容易になる。

Sources

コメントを残す