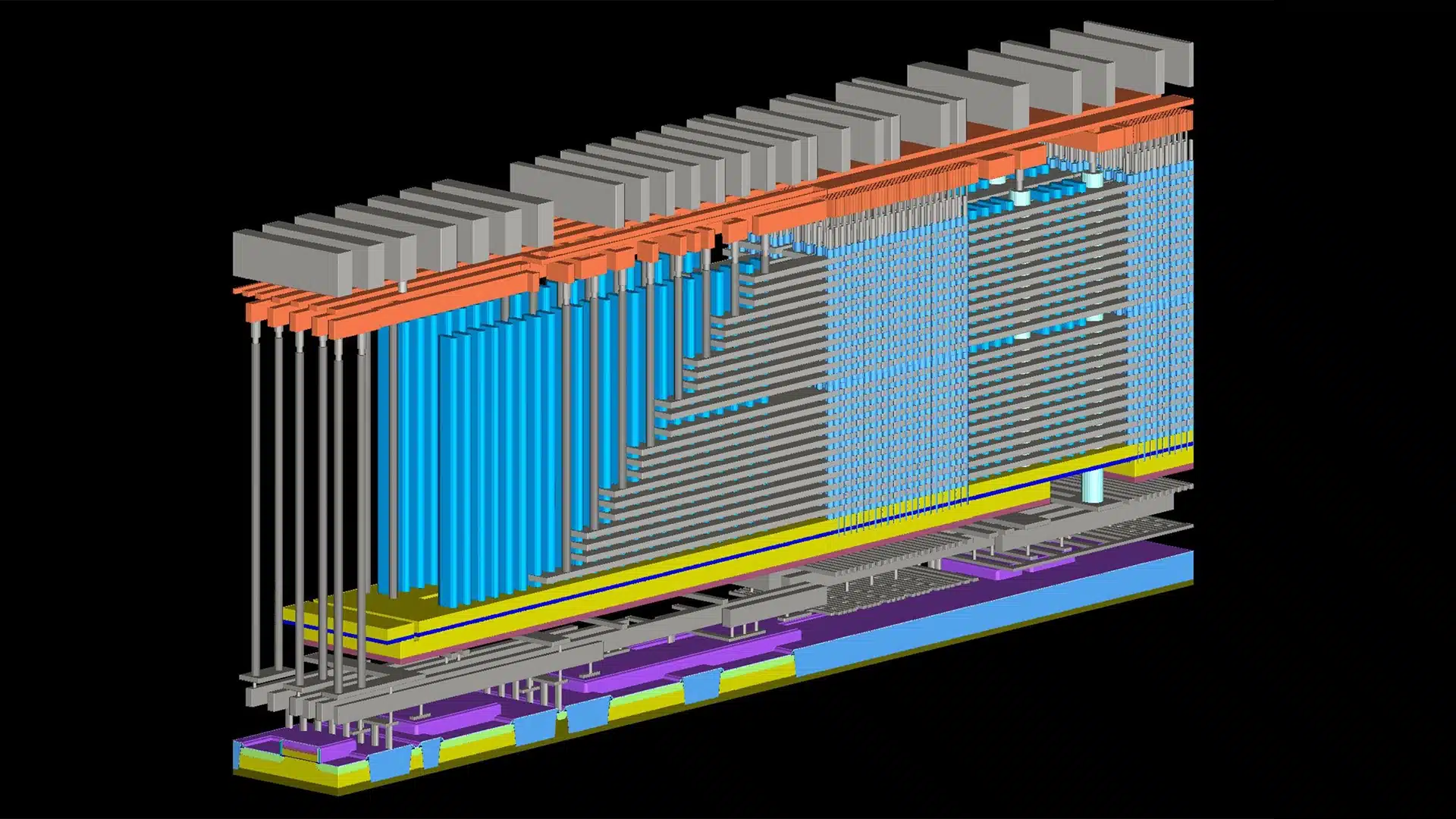

KIOXIAとWestern Digitalは、共同で開発した218層のアクティブレイヤーを持つ第8世代BiCS 3D NANDメモリデバイスを公開した。この新しいストレージデバイスは、3D TLCモードで1Tbの容量を提供し、3,200 MT/sのデータ転送速度を備えており、これにより、SSDメーカーは更に高性能で高容量のドライブを構築できるようになる。この高速なインターフェーススピードを実現するため、KIOXIAとWestern DigitalはYMTCのXtackingに類似したアーキテクチャを採用している。

218層のBiCS 3D NANDデバイスは、TLCとQLC構成をサポートし、ストレージ密度を最大化し、アドレス可能なアプリケーションを拡大するために開発された。新しいデバイスは、新しい「横方向シュリンク技術」を採用しており、ビット密度を50%以上増加させることが出来ると言う。フラッシュメモリICのアクティブレイヤー数が34%増加したことを考えると、50%のビット密度の増加は、NANDセルの横方向サイズを縮小して、1層あたりのセルの数を増やすことを示している。

一方、218層の3D NANDデバイスは、クワッドプレーンアーキテクチャを採用しており、プログラムと読み込み時間の高度な並列処理と高いパフォーマンスを実現している。また、218層の3D TLCデバイスには、3,200 MT/sの入出力インターフェースがある。これは、最高400 MB/sのピークの読み書き速度を提供することが出来る。高速なデータ転送速度は、PCIe 5.0インターフェースを搭載した高性能クライアントやエンタープライズSSDに役立つ。

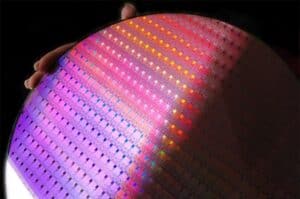

8世代BiCS 3D NANDメモリの主要なイノベーションは、完全に新しいCBA(CMOSダイレクトリーボンディングアレイ)アーキテクチャを採用している点だ。このアーキテクチャは、3D NANDセルアレイウエハーとI/O CMOSウエハーを最適なプロセス技術を使用して個別に生産し、それらを結合してビット密度を増加させ、高速なNAND I/Oスピードを提供する最終製品を作成する。しかし、KIOXIAとWestern Digitalは、CBAアーキテクチャの詳細や、I/O CMOSウエハーがページバッファ、センスアンプ、チャージポンプなどの他のNAND周辺回路を備えているかどうかについて、詳細を公開する必要がある。

メモリセルと周辺回路を個別に製造することは、クリーンルームの各セクションで最も効率的なプロセス技術を使用することができるため、いくつかの問題を解決する。この方法は、ストリングスタッキングなどの方法が業界で採用されるにつれて、さらなる利点をもたらす。

KIOXIAは、8世代BiCS 3D NANDメモリデバイスのサンプル出荷を選択された顧客に開始した事も、併せて発表した。ただし、同社が次世代フラッシュメモリの量産を開始する時期については言及されていない。3D NANDの新しいタイプを量産する前に、新しい製品を発表することは一般的だ。したがって、2024年に8世代BiCSが市場に登場することが予想される。

「技術開発におけるキオクシアとウエスタンデジタルのパートナーシップにより、業界最高ビット密度の第8世代のBiCS FLASH™を発表できることを大変嬉しく思います。CBA技術とスケーリングイノベーションを採用することで、スマートフォン、IoT機器やデータセンターまで、さまざまなデータセントリックなアプリケーションにも適応できる3次元フラッシュメモリ技術のポートフォリオを更に進化させることができました。弊社は特定のお客様に対して製品のサンプル出荷を既に開始しています」と、KIOXIA Corporationの技術統括責任者である百冨正樹氏は述べている。

3D NAND技術は、従来のプレーナー型フラッシュメモリ技術よりも高密度なデータストレージを可能にするため、現在、SSD(Solid State Drive)やスマートフォン、タブレットなどの多くのデバイスで使用されている。8世代BiCS 3D NANDメモリの登場により、ストレージ容量と性能が向上し、データ中心のアプリケーションの需要を満たすことができるようにることだろう。将来的には、この技術がますます進歩し、より高密度で高性能なストレージソリューションが開発されることが期待される。

Source

コメントを残す