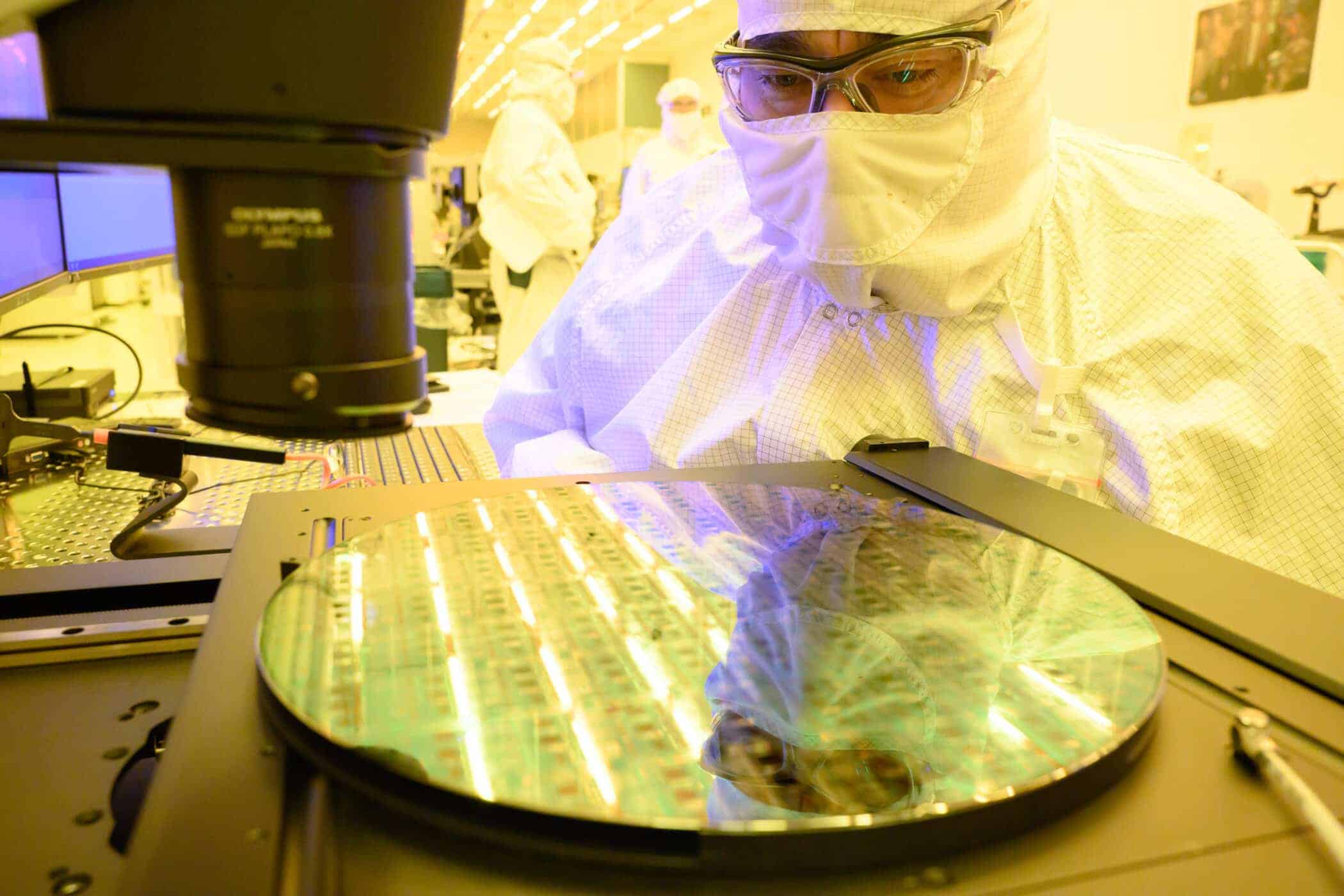

Intelは、同社の最新かつ最先端のチップ・パッケージング工場であるFab 9の解説を発表した。Fab 9は、Intelの先進的半導体パッケージング技術「Foveros」テクノロジーを使用したチップのパッケージングを担当する。Foverosテクノロジーは現在、Intelの最新クライアントCore Ultra(Meteor Lake)プロセッサーと、人工知能(AI)および高性能コンピューティング(HPC)アプリケーション向けのData Center Max GPU(Ponte Vecchio)の製造に使用されている。

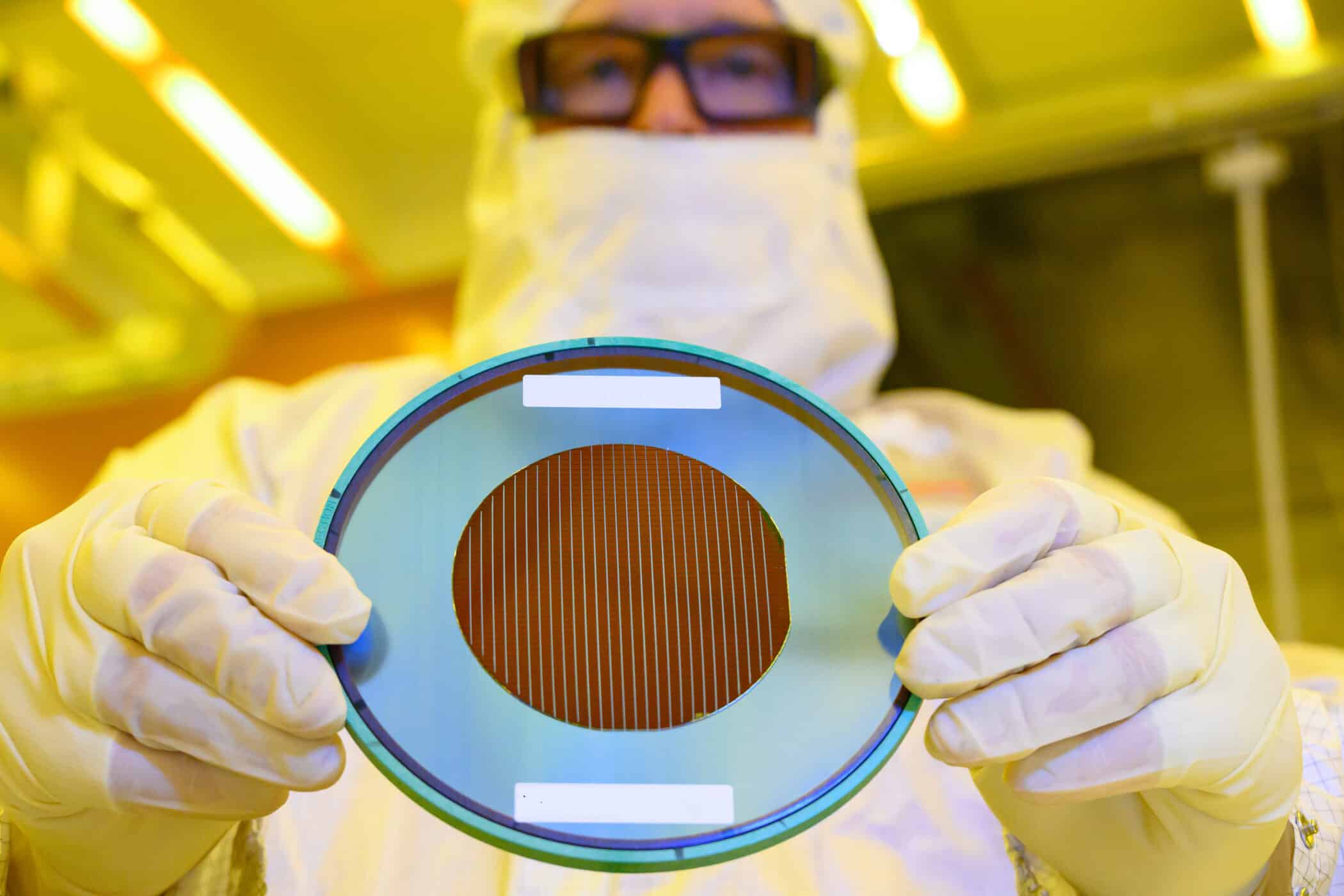

ニューメキシコ州リオランチョ近郊にあるこの工場は、Intelが建設と設備に35億ドルを費やした。これまでに建設された最先端パッケージング施設の中で最も高額と思われるこのファブの建設費の投資額は、Intelが最先端パッケージング技術と生産能力に関していかに真剣であるかを物語っている。Intelの製品ロードマップでは、今後マルチダイ/チップレット設計の大幅な活用が求められており、Intel Foundry Servicesの顧客のニーズと相まって、同社はFoveros、EMIB、その他の先端パッケージング技術の生産量の大幅な急増に備えている。

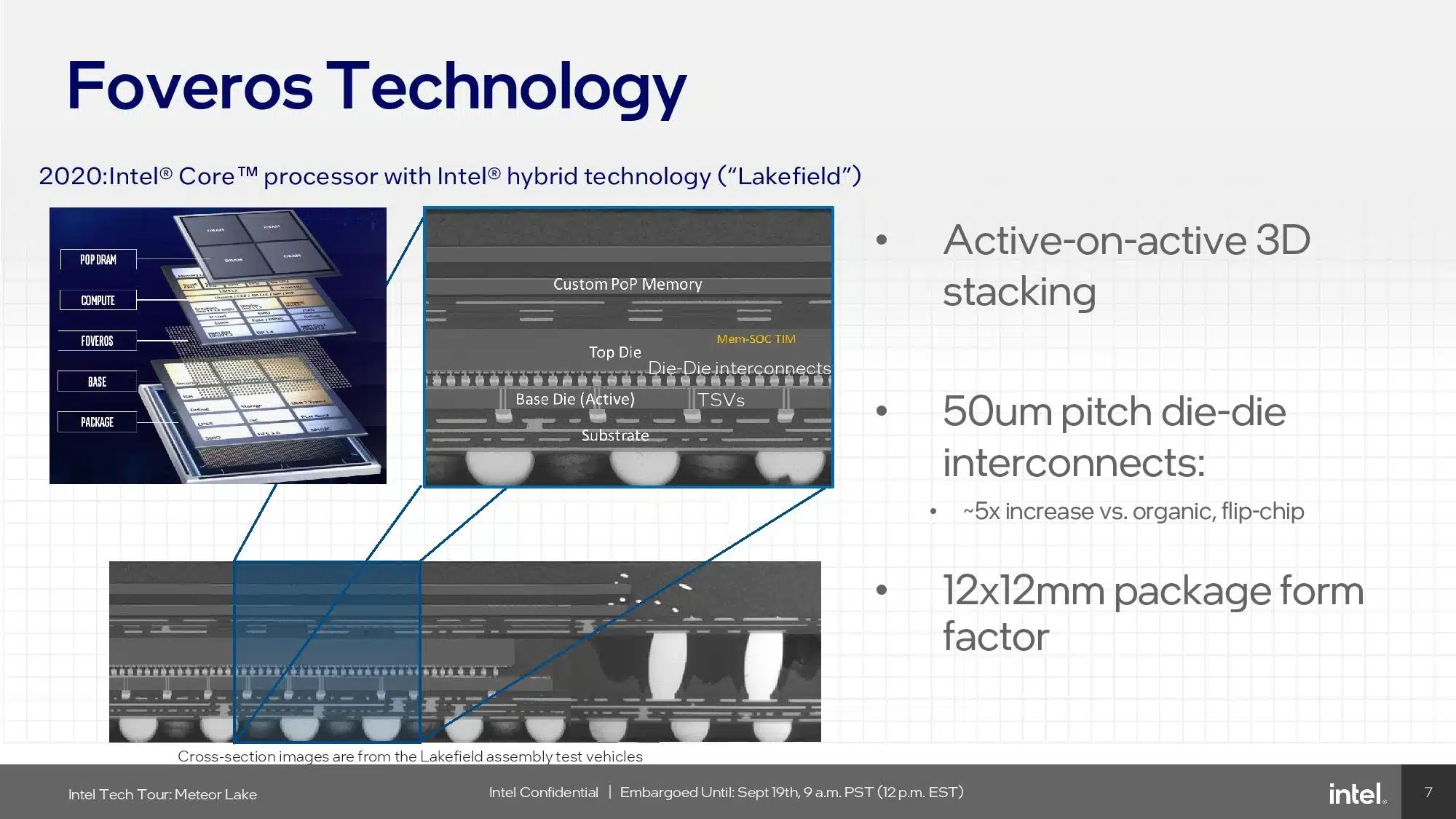

IntelのFoverosは、同社の低消費電力22FFL製造プロセスで製造されたベース・ダイと、その上に積層されたチップレット・ダイを使用するダイ・ツー・ダイ積層技術である。ベース・ダイは、それがホストするダイ間の相互接続のように機能したり、特定のI/Oやロジックを統合したりすることができる。現世代のFoverosは、36ミクロンという小さなバンプをサポートし、1平方ミリメートルあたり最大770の接続を可能にするが、バンプが最終的に25ミクロンや18ミクロンになるにつれて、この技術は接続密度と性能(帯域幅の点でも、サポートされる電力供給の点でも)を向上させる。

Foverosのベース・ダイは600mm2まで可能だが、600mm2より大きなベース・ダイを必要とするアプリケーション(データセンター向け製品など)では、インテルはCo-EMIBパッケージング技術を使って複数のベース・ダイをつなぎ合わせることができる。

ついにフル生産体制に入ったFab 9(かつての6インチ・ウェハー・リソグラフィー・ファブからその名を受け継いでいる)は、少なくとも今後数年間はIntelのFoverosチップ・パッケージの要になるだろう。同社はマレーシア(PGAT)にも「アドバンスド・パッケージング」能力を有しているが、これらの施設は現在EMIB生産用のツールしか備えていないため、IntelのFoverosチップ・パッケージングはすべてニューメキシコ・キャンパスで行われていることになる。Intelにとって初の大量Foverosパッケージング施設であるため、今回の能力増強により、IntelのFoverosパッケージング総処理能力は大幅に拡大することになるが、同社は具体的な生産量については明らかにしていない。

また、IntelのFab 11xが真隣にあるため、この2つの施設はIntel初の共同パッケージング先進パッケージングサイトでもあり、Intelは他のIntel工場から輸入しなければならないダイの数を減らすことができる。ただし、Fab 11xはIntel 4施設ではないため、Meteor Lakeの場合は22FFLベースダイの生産にのみ適している。Intelは、Intel 4で製造されたCPUダイ(オレゴン&アイルランド)と、TSMCで製造されたグラフィックス、SoC、I/Oダイ(台湾)をまだ輸入している。

Intelのエグゼクティブ・バイス・プレジデント兼チーフ・グローバル・オペレーションズ・オフィサーのKeyvan Esfarjani氏は、「本日、Intel初の量産半導体工場がオープンし、世界最先端のパッケージング・ソリューションを大規模に生産する唯一の米国工場となりました。この最先端技術により、Intelは他とは一線を画し、性能、フォーム・ファクター、設計アプリケーションの柔軟性において、すべて弾力性のあるサプライ・チェーンの中で、お客様に真の利点を提供することができます。ニューメキシコ・チーム、Intelファミリー全体、当社のサプライヤー、そしてパッケージング・イノベーションの限界を押し広げるために協力し、絶え間ない努力を続けている請負業者のパートナーの皆さん、おめでとうございます」と、述べている。

Sources

コメントを残す