IEDMにおいて、Intel Researchは、ムーアの法則がいかにまだ有効であるのか、そして同社が2030年までに1兆個のトランジスタを持つ次世代チップを提供する計画であることを改めて紹介した。これを実現するため、同社は将来のチップ設計の基礎となる、9つの研究を発表した。

内容としては、トランジスタ用の新しい2次元材料、チップレットとシングルダイプロセッサの性能と電力の差を大幅に縮小させる新しい3次元パッケージ技術、電源を切っても「忘れない」トランジスタ、トランジスタの上に直接積み重ねて1セルあたり1ビット以上記憶できる組み込みメモリなど、同社では革新的な研究が行われている。

研究成果が全て世に出るわけではなく、また実際に製品化されるとしても5〜10年後ではあるが、今後の半導体業界がどのように進んでいくのかを考える上で興味深い内容となっている。

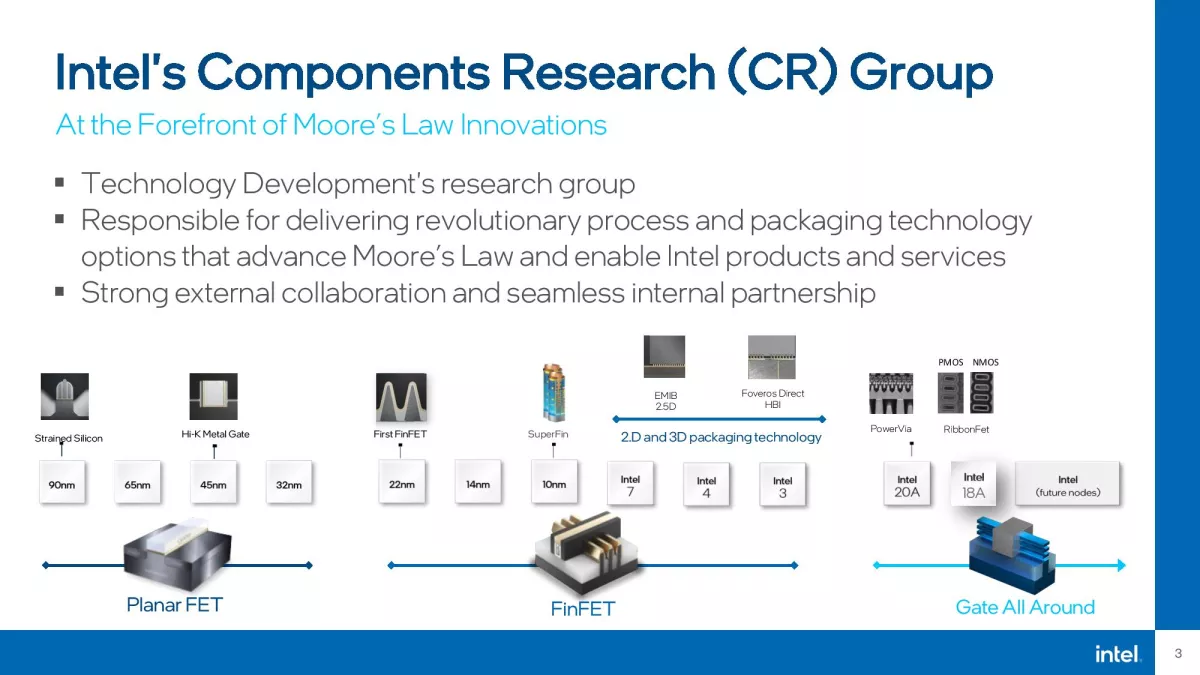

IntelのCR(Components Research)グループは、業界全体のトランジスタ設計に革命をもたらしたFinFET、歪みシリコン、Hi-Kメタルゲートなど、すでに市場に出ている革新的な技術で素晴らしい実績がある。同社はRibbonFET Gate All Around (GAA) トランジスタ、PowerVia バックサイドパワーデリバリ、EMIB、Foveros Direct など、すでにいくつかの技術をロードマップで明らかにしているが、これらもすべてこの研究グループから生まれた技術だ。

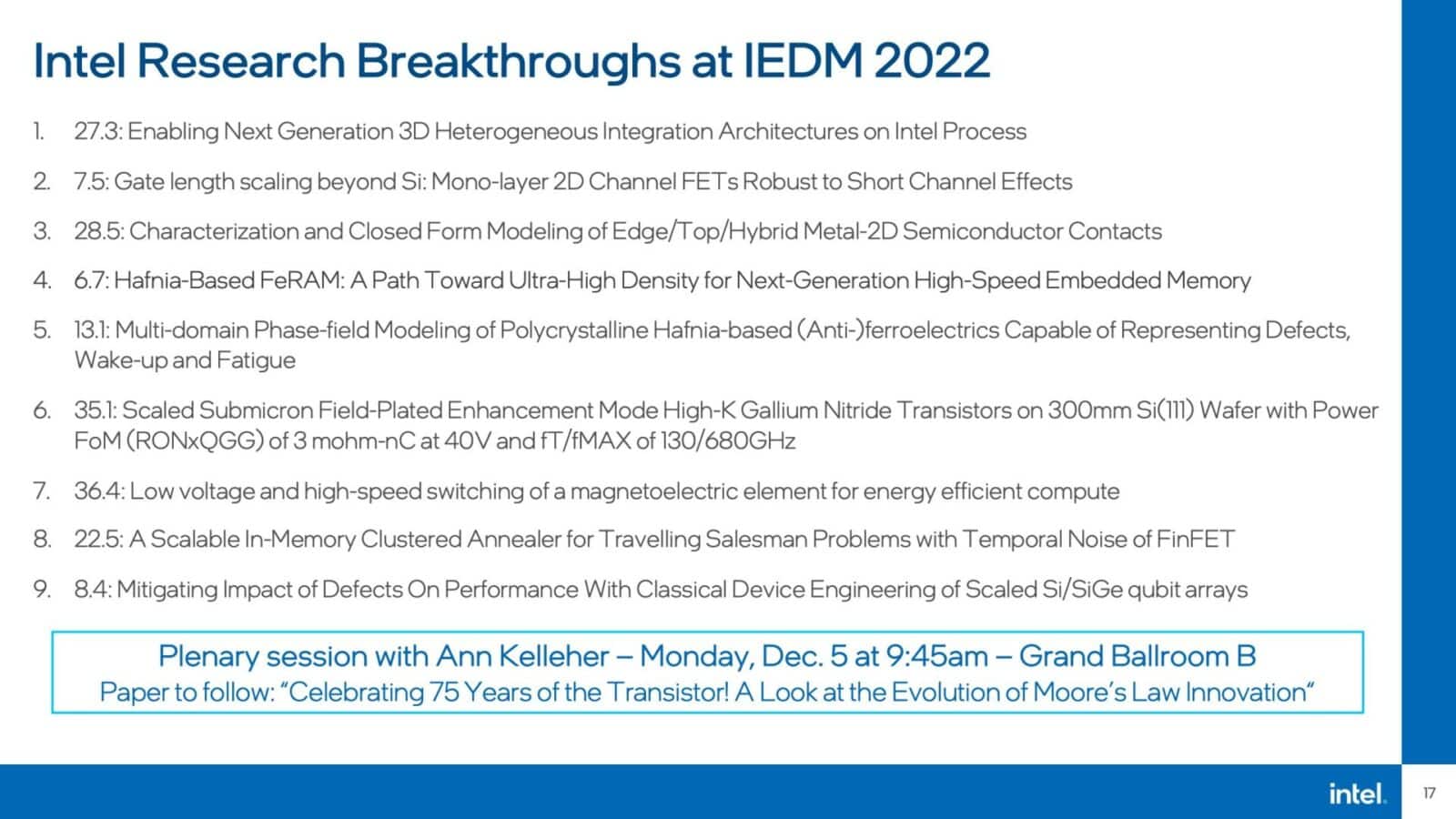

今回、同グループがIEDM(IEEE International Electron Devices Meeting)の68回大会で提出したのは9つの研究論文だが、そのうちのいくつかを以下に紹介する。

モノリシックプロセッサに匹敵する効率のチップレット設計

ムーアの法則が限界に近付くに連れ、半導体業界では高性能チップの実現のためにこれまでのモノリシックな設計から、チップレットベースの設計に移行している。AMDがその先陣を切り、大きな成果を見せているのは記憶に新しいだろう。

チップレットベース設計の最大の目標は、単一ダイのモノリシックプロセッサ内部のデータ経路の消費電力と性能(レイテンシ、帯域幅)の最良の特性を維持しながら、チップレットベースのアプローチを使用することで、最先端プロセスで製造された小型ダイによる歩留まりの向上や、密度の向上があまり見られない他の機能の一部に旧式の安価なノードを使用できるといった経済的メリットを利用することにある。

つまり現在、性能を争う舞台は、トランジスタの速度そのものからインターコネクトの性能へと移行しつつあり、シリコンインターポーザ(EMIB)やハイブリッドボンディング技術などの新技術が、経済性向上のために注目を集めている。

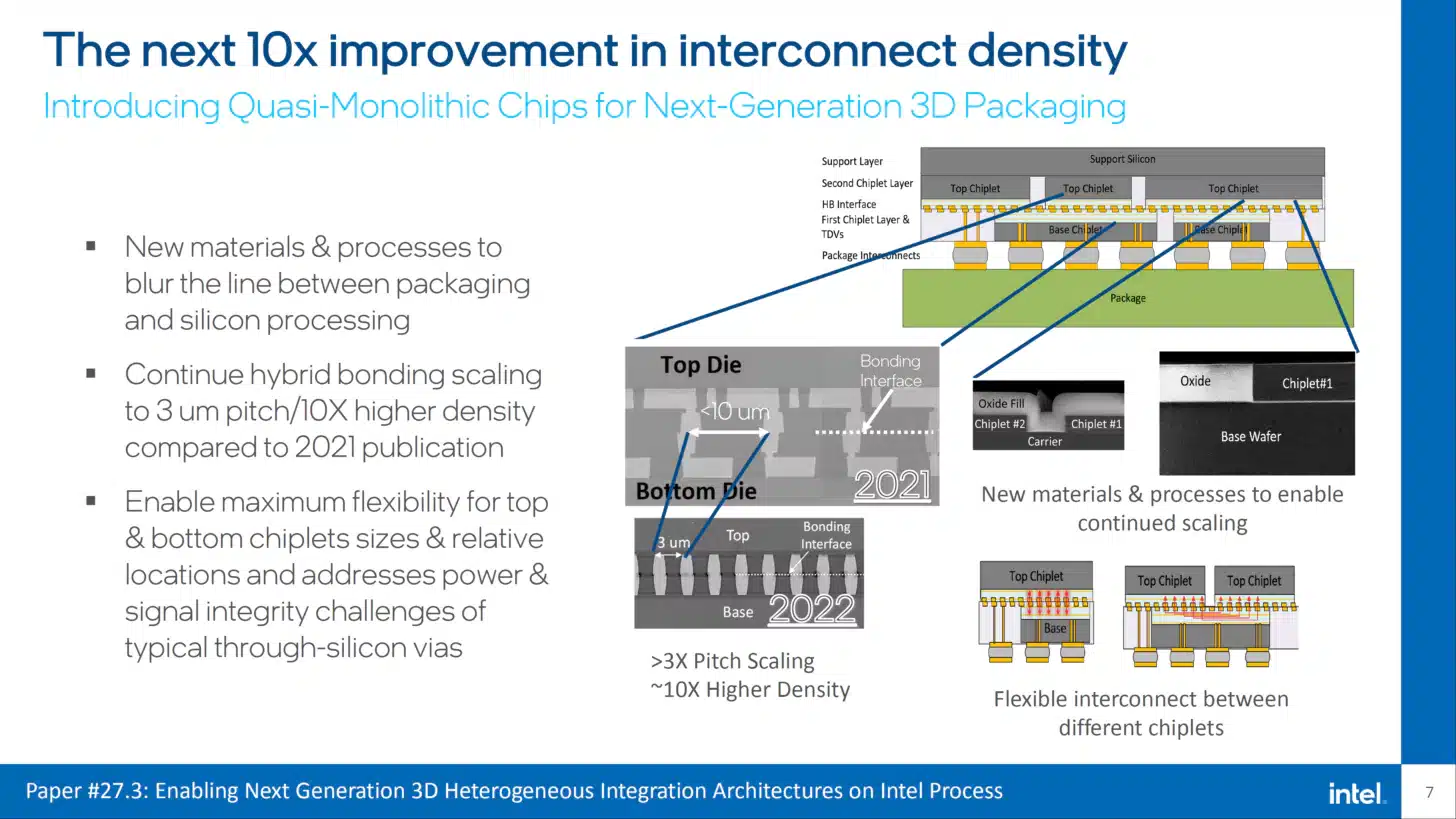

しかし、これらのアプローチでは、依然として性能、電力、コストのトレードオフが避けられない。Intelの新しい「準モノリシック・チップ」(QMC)3Dパッケージング技術は、これを解決しようとしている。その名の通り、IntelのQMCは、1つのダイに内蔵されたインターコネクトとほぼ同じ特性を提供することを目指している。

QMCは、3ミクロン以下のピッチを特徴とする新しいハイブリッドボンディング技術で、Intelが昨年のIEDMで提出した研究に対して、電力効率と性能密度を10倍向上させる結果となった。その前の論文では、10ミクロンピッチのアプローチを取り上げており、すでに10倍の改善となっていた。このように、Intelはわずか数年で100倍の向上への道筋を見出したわけで、同社のハイブリッドボンディングへの取り組みが急速に加速していることが分かる。QMCでは、上の図のように、複数のチップレットを垂直に積み重ねることも可能だ。

この論文では、1平方ミリメートルあたり数十万という驚異的な相互接続密度と、モノリシックプロセッサに匹敵する消費電力(ビットあたりのピコジュール(Pj/b)で測定)の概要が示されている。さらに、この新しい論文では、このようなデバイスの製造に使用されるであろういくつかの新しい材料とプロセスの概要を示し、現実のデバイスへの道を開いている。

新たなトランジスタ材料

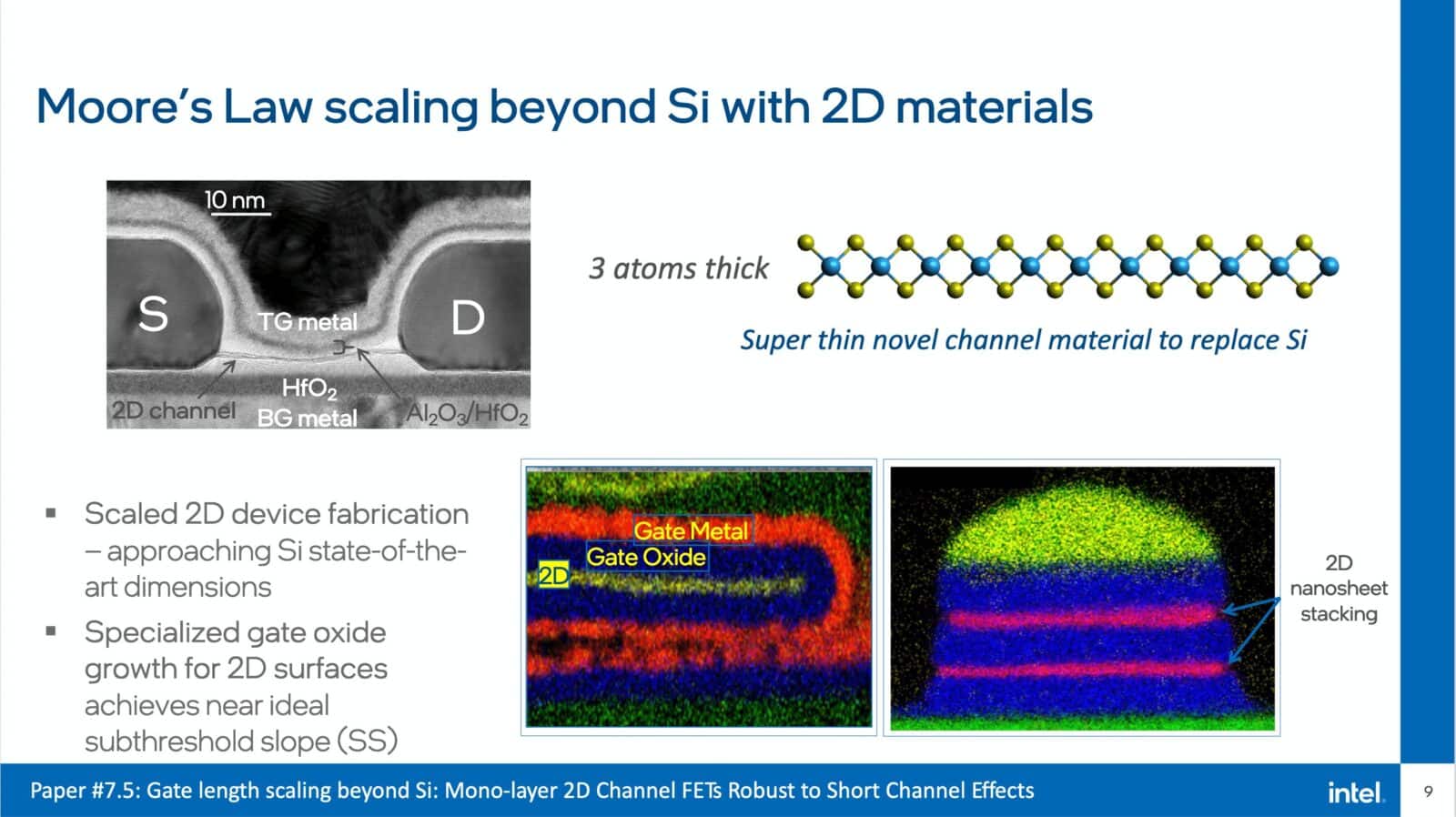

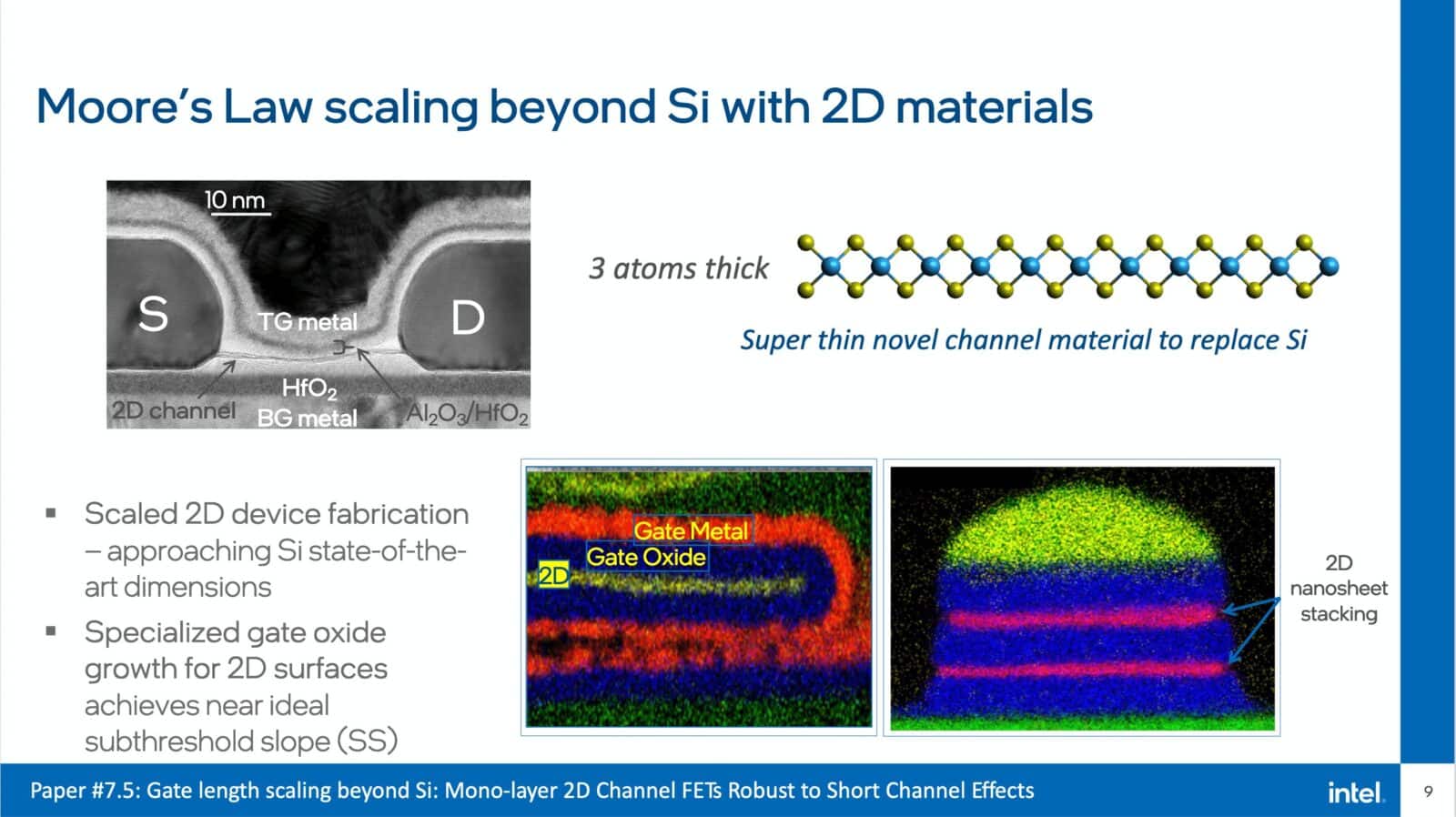

Intelがこれまでに明らかにしているロードマップでは、ナノメートルを超えて、オングストロームレベルの微細化への道筋が描かれているが、微細化を継続するにこれまでとは全く異なるアプローチが必要だ。業界の大半は、将来的に2次元原子チャネルに移行するべく研究を続けているが、そのためにはまだ長い道のりが待っている。

シリコンのような現在のチップ材料は、3次元結晶で構成されているため、原子が3次元すべてで結合しており、微細化には根本的な限界がある。一方、2次元材料は、すべての原子が1つの平面で結合しているため、原子そのものの厚みで機能を実現できるのが魅力だ。

そこでIntelは、3次元GAAトランジスタの材料として2次元材料を研究している。現在のGAAは、水平に積み重ねたシリコン・ナノシートで構成されており、各シリコン・ナノシートはゲートで完全に囲まれている。この「ゲート・オール・アラウンド(GAA)」技術により、トランジスタのスイッチオフを妨げる電圧リークを低減することができる。FinFETトランジスタのように、ゲートがチャネルの3面を囲んでいる場合でも、トランジスタが小型化するにつれて、この問題は大きくなっている。

Intelは、GAA設計をRibbonFETと名付け、現在2024年前半にリリースする予定だ。しかし、RibbonFETを超えるにはさらなるイノベーションが必要であり、今回の2次元材料の研究はそのためのものとなる。

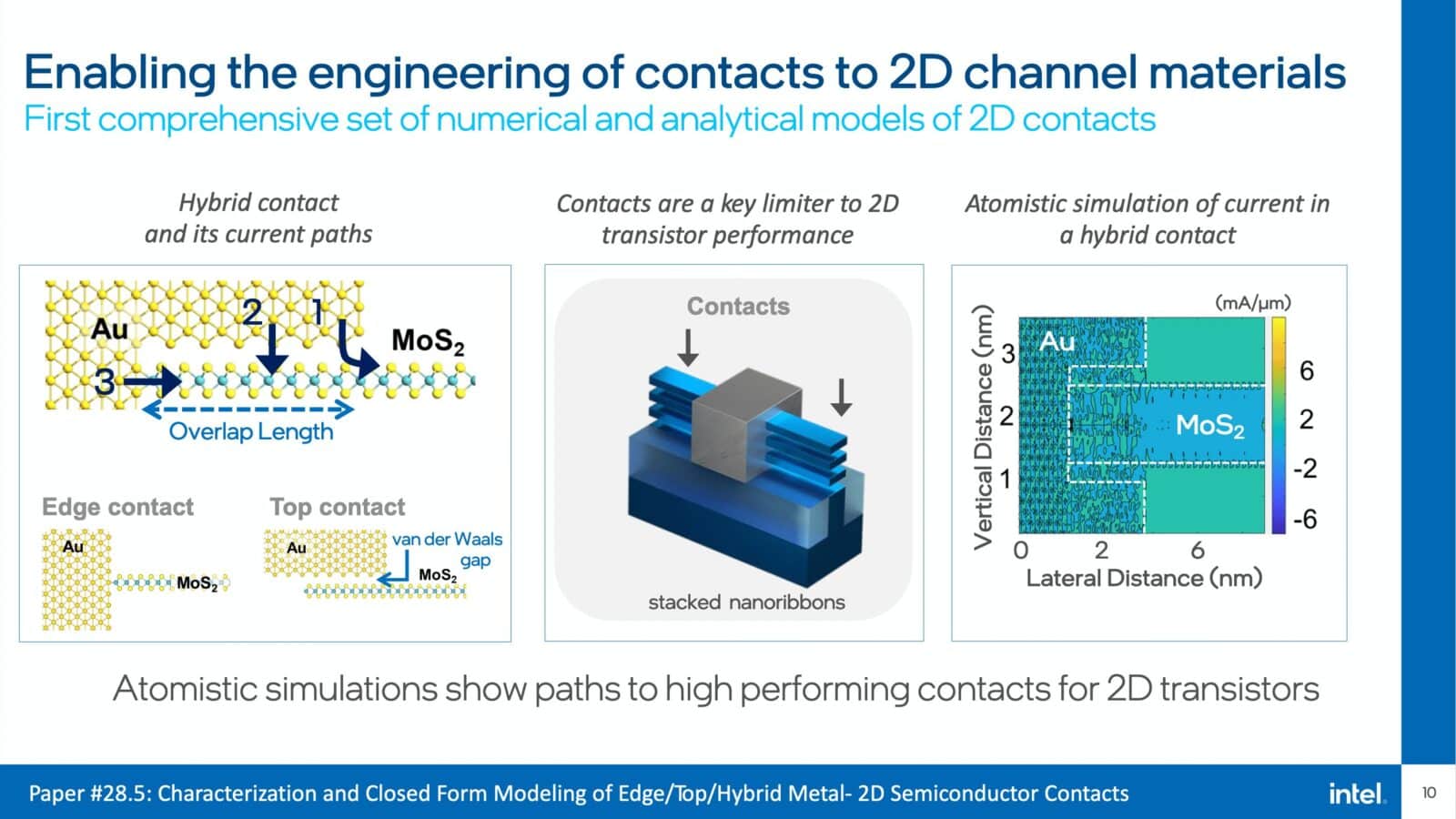

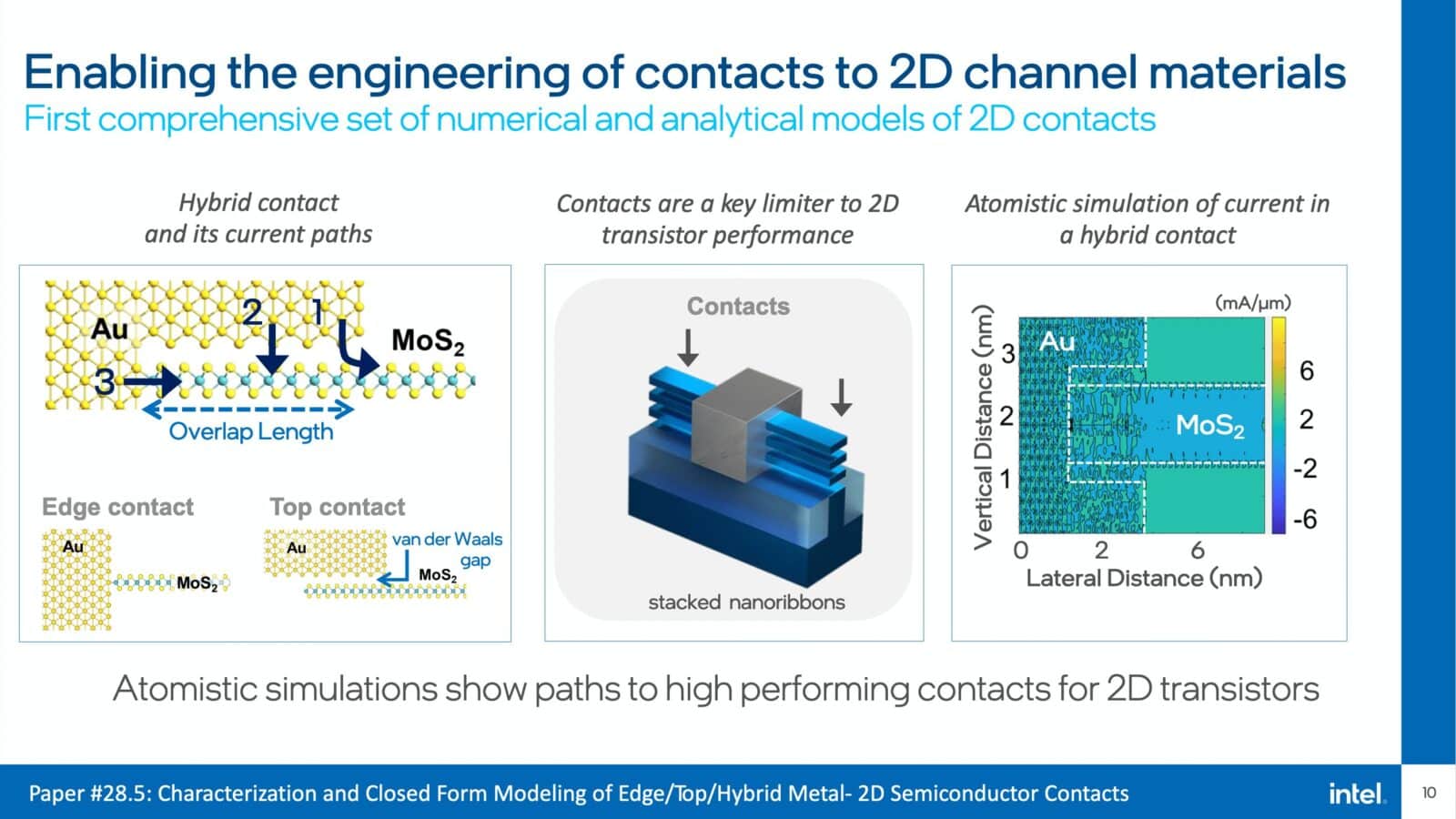

Intelの論文では、厚さわずか3原子のチャネル材料(ナノシート/ナノリボン)を用いたGate All Around(GAA)積層ナノシート構造について述べており、室温で低リーク電流で動作させることができる。

2次元チャネル材料は薄いため、ナノリボンとの電気的接続を確立するのは困難だ。そこでIntelは、2D材料の電気接触トポロジーのモデル化も行った。これは、2D材料の特性とその機能を理解するための重要なステップであり、その結果、さらなる進化を正確にモデル化することが可能になる。

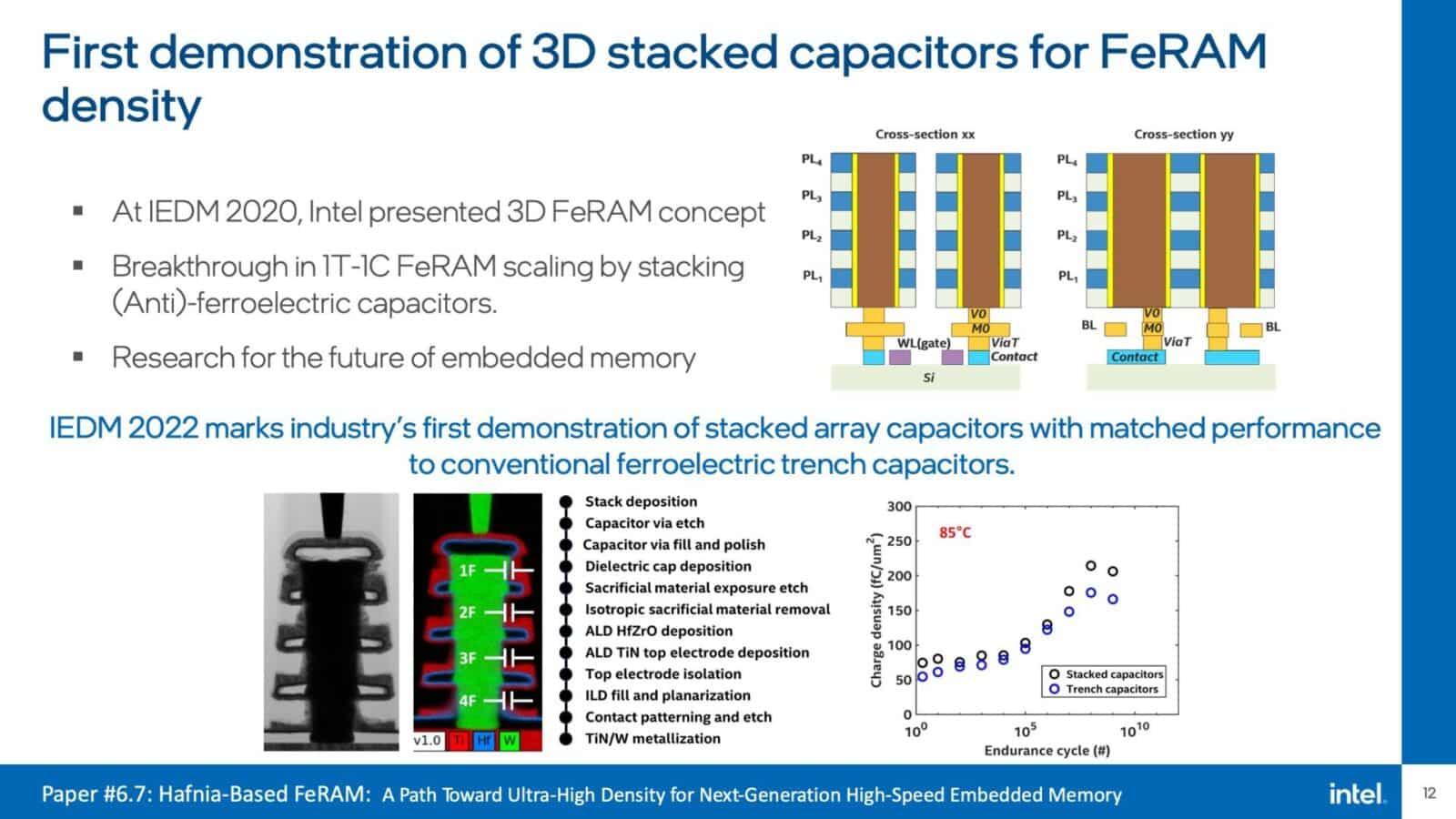

「忘れない」メモリ

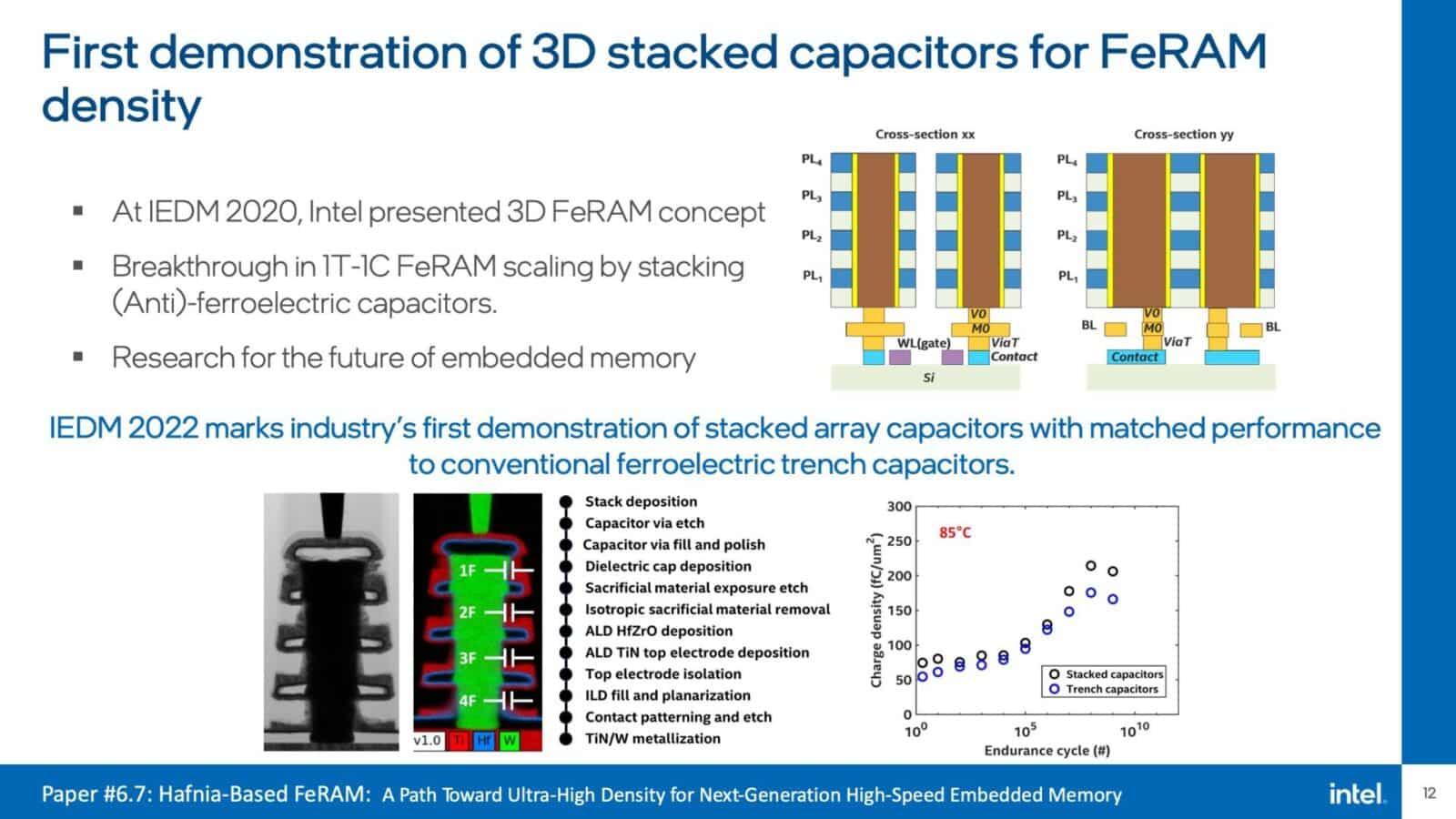

Intelはまた、3D積層型強誘電体メモリの世界初の機能デモを実施した。この技術の最も印象的な点は、強誘電体トレンチキャパシタをロジックダイ上のトランジスタの上に垂直に積み重ねることができることだ。これにより、L1キャッシュやL2キャッシュに使用されるSRAMのような他のタイプの組み込みメモリで見られるように、メモリが独立した領域にあるのではなく、ロジック素子の上にレイヤー化することができる。

また、強誘電体メモリは、NANDフラッシュと同様の機能、つまり通常は1ビットしか格納できない構造で複数ビットのデータを格納することが可能である。今回、Intelは1トレンチあたり4ビットのデータを格納できることを実証した。

当然ながら、このアプローチでは帯域幅とメモリ密度の両方が向上し、レイテンシが減少するため、より大規模で高速なオンチップキャッシュを実現できる。

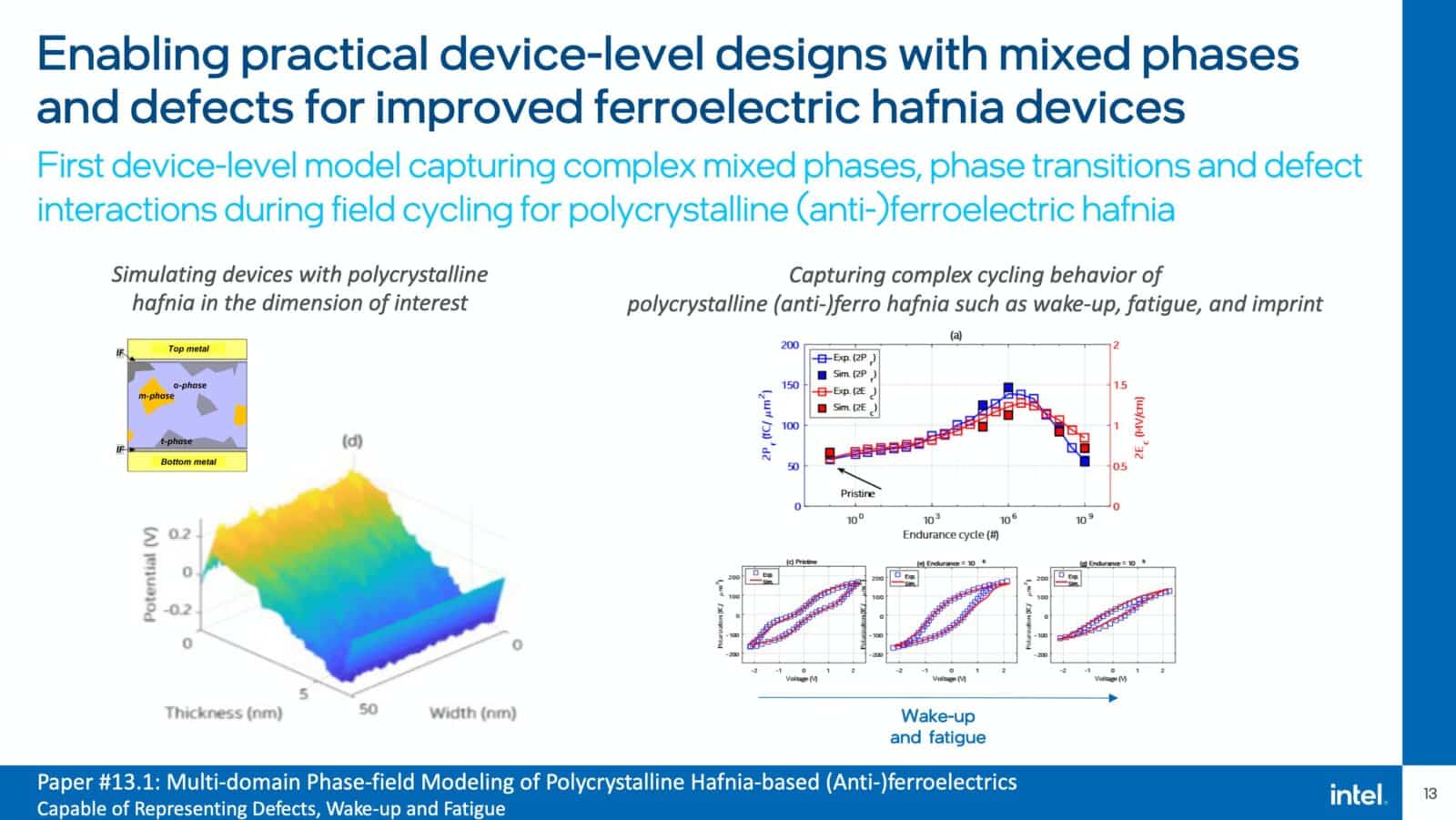

2次元構造の電気接点のモデリングと同様に、Intelは強誘電体ハフニアデバイスの混合相と欠陥のモデリングも行い、これはIntel自身の研究開発プロセスを促進することになる。

また、Intelは「忘れない」、つまり電源を落としてもデータ(オン/オフ状態)を失わないトランジスタの研究も行っている。これは、NANDのように電源を切っても状態を保持できる不揮発性ストレージと同じようなものだが、ロジックトランジスタという形で提供される。Intelは、この技術を室温で使うための3つのロードブロックのうち2つをハードルした、と述べている。

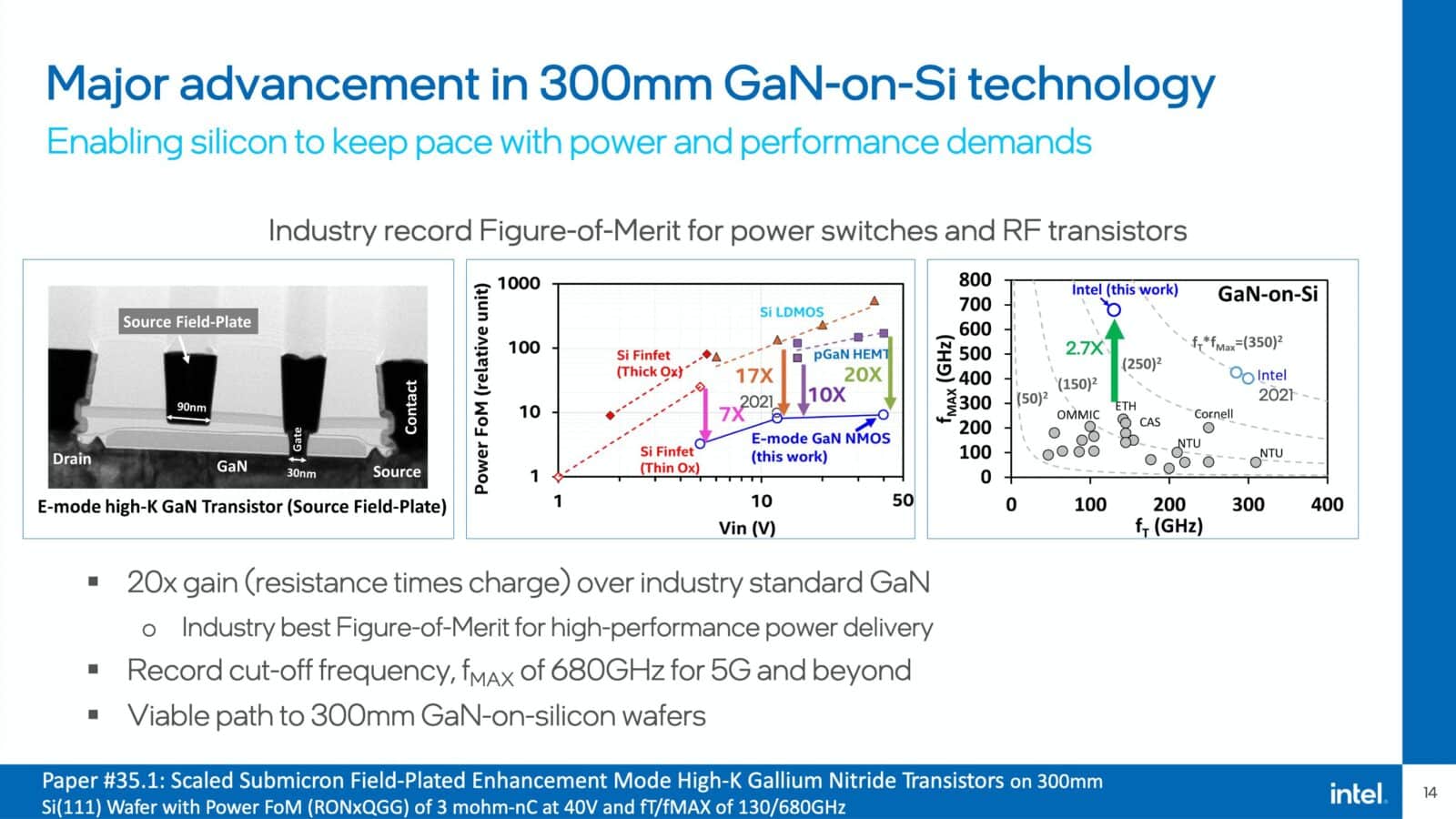

このほかにも、5G以降の技術を可能にするGaNオンシリコンウェハーや、量子コンピューティングのためのよりよい量子ビットを作るための量子情報の保存方法など、Intelの研究分野の概要を紹介する論文が発表された。

同社によるプレスリリースは以下の通りとなる。

Intelの研究がムーアの法則を促進し、2030年までに1兆個のトランジスタを実現する道を開く

トランジスタ誕生75周年を迎えるIEDM 2022で、Intelはパッケージング技術で新たに10倍の密度向上を目指し、わずか3原子の厚さの新材料を使ってトランジスタのスケーリングを進めます。

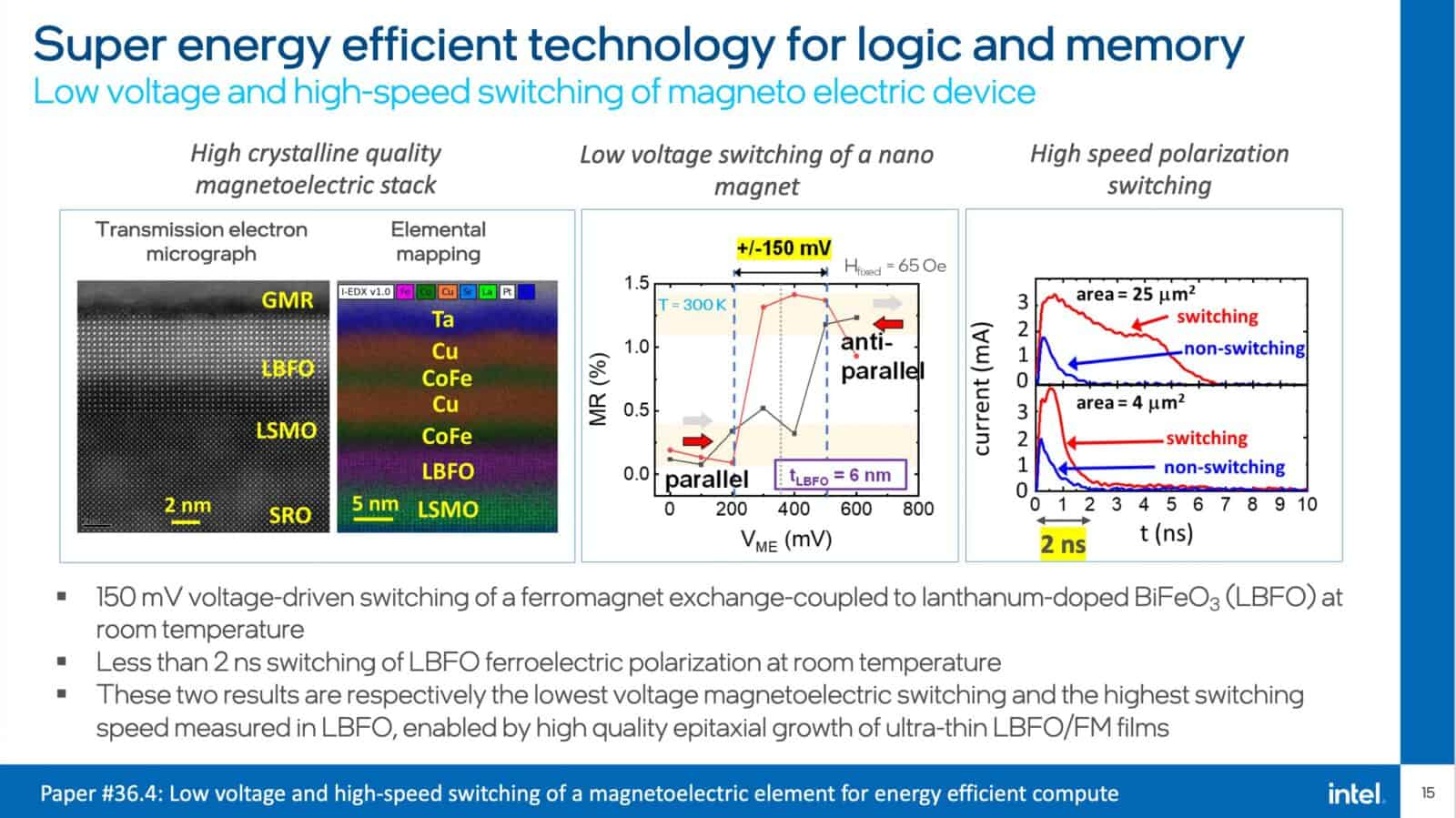

本日、Intelは、ムーアの法則を維持し、今後10年間で1兆個のトランジスタをパッケージに搭載するためのイノベーション・パイプラインに拍車をかける研究のブレークスルーを発表しました。IEEE International Electron Devices Meeting (IEDM) 2022において、Intelの研究者は、密度を新たに10倍向上させた3Dパッケージング技術の進歩、RibbonFETを超える2Dトランジスタスケーリング用の新規材料(厚さわずか3原子の超薄型材料を含む)、より高性能なコンピューティングのためのエネルギー効率とメモリにおける新しい可能性、量子コンピュータの進歩について発表しました。

トランジスタの発明から75年、ムーアの法則を推進する技術革新は、指数関数的に増大する世界のコンピューティング需要に対応し続けています。IEDM 2022において、Intelは、現在および将来の障壁を打破し、この飽くなき需要に応え、ムーアの法則を今後何年にもわたって維持するために必要な先見性と具体的な研究の進展の両方を展示します。

Intel副社長兼コンポーネント・リサーチ&デザイン・イネーブルメント担当ジェネラル・マネージャー Gary Patton氏

IEDMでの出来事:トランジスタの誕生75周年を記念して、Intel社取締役副社長兼技術開発本部長のAnn Kelleher博士がIEDMのプレナリーセッションで講演を行ないます。Kelleher博士は、産業界の継続的なイノベーションのための道筋を説明します。それは、世界中で高まるコンピューティングへの需要に対応し、ムーアの法則に沿ったペースでより効果的にイノベーションを進めるためのシステムベースの戦略を中心にエコシステムを結集させることです。このセッション、「トランジスタ誕生75周年を迎えて!A Look at the Evolution of Moore’s Law Innovation」は、12月5日(月)午前9時45分(太平洋標準時)より行われます。

なぜ重要なのか?ムーアの法則は、データ消費の急増と人工知能(AI)強化の推進により、過去最大の需要加速をもたらす世界の飽くなきコンピューティングニーズに対応するために不可欠なものです。

継続的なイノベーションは、ムーアの法則の基礎となるものです。歪みシリコン、Hi-Kメタルゲート、FinFETなど、パソコン、グラフィックス・プロセッサ、データセンターにおいて、過去20年にわたり電力、性能、コストを改善し続けてきた重要なイノベーションのマイルストーンの多くは、Intelのコンポーネント研究グループから始まっています。RibbonFETゲートオールアラウンド(GAA)トランジスタ、PowerVia裏面電力供給技術、EMIBやFoveros Directなどのパッケージングブレイクスルーなど、さらなる研究が現在ロードマップ上にあります。

IEDM 2022において、Intelのコンポーネント研究グループは、ムーアの法則を継続するために、次の3つの主要分野でイノベーションに取り組む姿勢を示しました。すなわち、チップレットをシームレスに統合できる新しい3Dハイブリッド ボンディング パッケージング技術、1チップにより多くのトランジスタを搭載できる超薄型2D材料、より高性能なコンピュータを実現するエネルギー効率とメモリにおける新しい可能性、などです。

どのように実現したか: コンポーネント研究グループの研究者は、パッケージングとシリコンの境界線を曖昧にする新材料と新プロセスを特定しました。 ムーアの法則をパッケージ上の1兆個のトランジスタに拡張するための重要な次のステップを明らかにします。これには、さらに10倍の相互接続密度を達成し、準モノリシック・チップにつながる先進のパッケージングが含まれます。Intelの材料イノベーションは、わずか3原子厚の新材料を使用してトランジスタのスケーリング要件を満たすことができる実用的な設計の選択肢を特定し、RibbonFETを超えるスケーリングの継続を可能にしました。

Intel、次世代3次元実装用準モノリシック・チップを発表

- IEDM 2022で発表されたIntelの最新のハイブリッドボンディング研究では、IntelのIEDM 2021の研究発表に比べて、電力と性能の密度がさらに10倍向上していることが示されています。

- 3 umピッチへの継続的なハイブリッドボンディングのスケーリングにより、モノリシックシステムオンチップ接続で見られるものと同様のインターコネクト密度と帯域幅を達成しました。

Intelは、より多くのトランジスタを1つのチップに搭載するために、超薄型の「2D」材料に注目しています

- Intelは、わずか3原子厚の2次元チャネル材料を用いてゲート全周積層ナノシート構造を実証するとともに、ダブルゲート構造上のトランジスタの理想に近いスイッチングを室温で低リーク電流で達成しました。これは、GAAトランジスタを積層し、シリコンの基本的な限界を超えるために必要な2つの重要なブレークスルーです。

- また、研究者らは、高性能でスケーラブルなトランジスタチャネルへの道をさらに開く可能性のある2次元材料への電気的接触トポロジーを初めて包括的に解析したことを明らかにしました。

Intelは、より高性能なコンピューティングのために、エネルギー効率とメモリに新たな可能性をもたらします。

- チップ面積をより効果的に使用するために、Intelはトランジスタの上に垂直に配置できるメモリを開発し、スケーリングを再定義しました。業界初、Intelは従来の強誘電体トレンチ・コンデンサーの性能に匹敵する積層強誘電体コンデンサーを実証し、ロジック・ダイ上にFeRAMを構築するために使用することができます。

- 業界初のデバイスレベルのモデルは、強誘電体ハフニアデバイスの改良のために混合相と欠陥を捕捉し、新しいメモリと強誘電体トランジスタを開発するための業界ツールのサポートにおいてIntelに大きな進展をもたらしました。

- 5G 以降の移行と電力効率の課題解決に一歩近づくために、Intelは 300 ミリメートル GaN-on-Silicon ウェハーへの実現可能なパスを構築しています。この分野におけるIntelの躍進は、業界標準のGaNに比べて20倍の利得を示し、高性能電力供給における業界記録の数字を打ち立てています。

- Intelは、超エネルギー効率の高い技術、特に電源を切ってもデータを保持する「忘れない」トランジスタでブレークスルーを起こしています。すでにIntelの研究者は、室温での完全実用化を妨げている3つの障壁のうち2つを突破しています。

Intelは、量子コンピューティングのためのより良い量子ビットを提供するためのブレークスルーで、物理学の新しい概念を紹介し続けています。

- Intelの研究者は、量子データに影響を与える環境妨害として作用する可能性のあるさまざまな界面欠陥について理解を深め、量子情報のより良い保存方法を見つけるために研究を行っています。

コメントを残す