IBMは、同社が明らかにしていたロードマップが予定通り進んでいることを再確認し、本日、新たなロードマップと共に、1,121個の量子ビットを持つ「Condor」量子プロセッサーと、”ユーティリティ・スケール”を達成したという量子プロセッサー「Heron」、そしてこのHeronを中心としたモジュール式で拡張可能なスーパーコンピューティングのコア・ビルディング・ブロック「IBM Quantum System Two」を発表した。

IBM QuantumのJay Gambetta副社長(IBMフェロー)はブログの中で、これらの新しい量子プロセッサーと、今日発表された他の先進的なソフトウェア・ツールは、量子コンピューティングの基礎研究から実用化への移行を意味すると書いている。

量子ビットと論理量子ビット

量子コンピュータの基礎となる量子ビットは、その扱うほぼ全ての局面でエラーが発生しやすい。量子ビットの初期状態の設定、その状態の維持、演算の実行、状態の読み出しなど、すべてに誤差が生じ、量子アルゴリズムが有用な結果を出せなくなる可能性がある。そのため、量子ハードウェアを製造するすべての企業は、このような誤差を抑えることに主眼を置いており、この点で大きな進歩を遂げている。

このような進歩により、既存のハードウェアでより単純な量子アルゴリズムを実行することが可能になった。そして、この可能性は、今後数年間でおそらく期待できる改良のおかげで、さらなるアルゴリズムに拡大する可能性が高い。

しかし長期的には、プロセッサが何時間もかけて何十億もの演算を必要とするような複雑なアルゴリズムを成功させられるほど、量子ビット・ハードウェアのエラー率が低くなることはないだろう。そのためには、エラー訂正された量子ビットが必要だというのが一般的な認識だ。論理量子ビットと呼ばれる量子ビットが持つ量子情報を、複数のハードウェア量子ビットに分散させるのだ。追加の量子ビットは、論理量子ビットのエラーを監視し、その訂正を可能にするために使用される。

論理量子ビットを使った計算には2つのことが必要である。ひとつは、個々のハードウェア量子ビットのエラー率が十分に低く、新たなエラーが発生する前に個々のエラーを特定し修正できることである。(部分的な効率ではあるが、ハードウェアの性能は十分であることが示唆されている)。各論理量子ビットが機能するためには複数のハードウェア量子ビットが必要だからだ。有用な数の論理量子ビットをホストできるマシンを作るには、100万個のハードウェア量子ビットが必要だという試算もある。

IBMは現在、10年後までには有用な数の論理量子ビットを持つことができるようになると予想している。

Gambetta氏によれば、同社はハードウェアを準備するために2つのアプローチをとっている。そのひとつが、高品質の量子ビットを安定して大量に製造する能力の開発である。今回発表したCondorはその開発が順調に進んでいることの証左だ。

IBMが取り組んでいる2つ目の側面は、個々の、あるいは2つ1組の量子ビットに対して演算を行う際に発生するエラーを制限することである。ゲートと呼ばれるこれらの操作は、それ自体がエラーを起こしやすい。また、量子ビットの状態を変化させると、クロストークと呼ばれる現象で、隣接する量子ビットに影響を及ぼす微妙な信号が発生する可能性がある。

この改良の多くは、量子ビットにチューナブル・カプラーを導入したことに起因する。これにより、すべてのゲート動作が高速化され、10倍になったものもある。量子ビットを扱う時間が短ければ短いほど、エラーが発生する機会は少なくなる。

IBM Condor

Condorは、1,121個の超伝導量子ビット・プロセッサーである。前モデルの「Osprey」の2倍以上の量子ビットを持ち、これまで発表された中で最大のトランスモンベースの量子プロセッサーであり、IBMの量子チップ設計の飛躍を象徴するものだ。Condorは量子ビット密度が50%向上し、1つの希釈冷凍機内に1マイルを超える高密度極低温フレックスIO配線を備えている。Condorは、スケールを解決し、将来のハードウェア設計に情報を提供するマイルストーンとして機能する。

IBM Heron

Heronは、IBMの量子プロセッシング・ユニット(QPU)シリーズの最新作だ。Eagleと名付けられた前モデルの127個から向上し、調整可能なカプラを備えた133個の固定周波数量子ビットを搭載する事を特徴としている。デバイス性能は前モデルのEagleから3~5倍となり、事実上クロストークを排除している。特筆すべきはエラー率が大幅に改善されており、Heronは前モデルと比較して5倍の改善が見られるという。量子ビットには計算タスクに必要な以上の情報が含まれているが、その情報は破損する可能性があるため、Heronの主張するエラー率の改善は実用的な量子コンピュータの実現に重要な要素となる。

また、IBMは今後の計画として、156量子ビットのFlamingoチップを明らかにしている。大きな違いは、各世代で最大ゲート数を2024年の5,000から2028年の15,000に引き上げることだ。また、このチップは最終的に最大7個のQPU、合計1,092量子ビットのクラスタサイズをサポートする予定だ。

これらのチップはすべてエラー緩和型に分類され、各世代が量子ビットの効率を向上させるためにエラー率の低減も目指すことを示唆している。

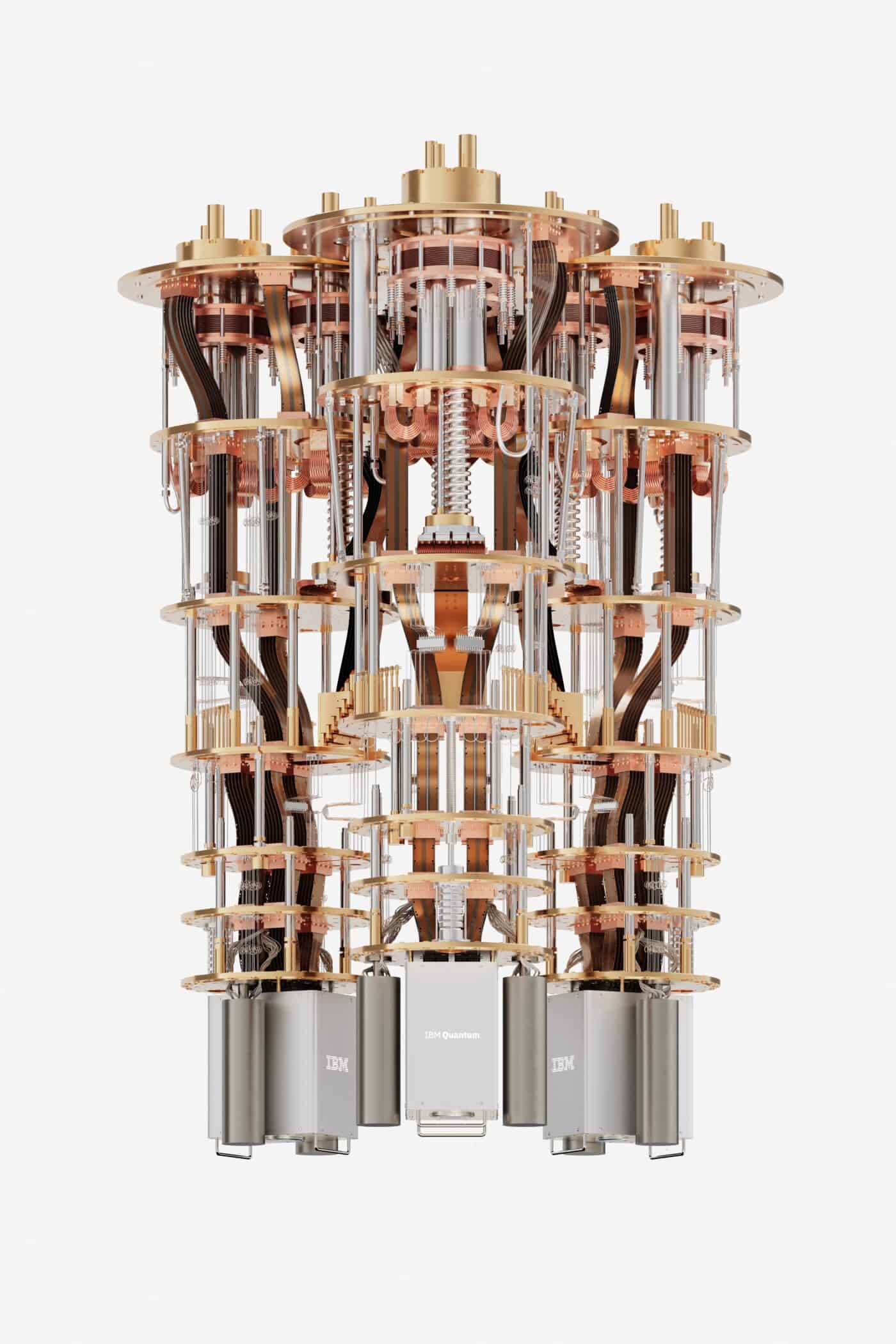

IBM Quantum System Two

HeronはIBMのQuantum System Twoコンピュート・クラスターに搭載され、量子、古典、量子ビット制御エレクトロニクスを組み合わせた、成長を目的としたモジュラー・システムとなる。詳細はまだ不明だが、IBMのQuantum System Twoコンピュート・クラスタは高さ5メートルで、多くの量子システムと同様、動作には極低温冷却を必要とする。

初期システムはニューヨーク州ヨークタウン・ハイツに設置され、当初はIBMのHeronプロセッサーを3つ搭載し、合計399個のローカル量子ビットを搭載する予定だ。

System Twoは将来の量子スーパーコンピューターのビルディングブロックとして設計されているため、将来のQPU設計と前方互換性を持つように設計されている。

しかしIBMは、量子ビット数は1つの要素に過ぎないと強調している。過去に議論したように、コヒーレンスや量子ビットの質といった要素は、量子マシンの基本的な能力にしばしばより大きな影響を与える。そのためIBMは、実現可能な量子回路のサイズを優先している。

IBMは2024年末までに、各Heronプロセッサが1つの量子回路で5,000回の演算を実行できるようになると主張している。

2028年以降に目を向けると、IBMは2029年からStarling QPUでエラー訂正の領域に入ると予想している。IBMは、このチップが200個の論理量子ビットから1億ゲートを絞り出すだろうと予測している。2033年以降に目を向けると、IBMは10億ゲートの回路が可能な2,000量子ビットのQPU、Blue Jayの発売を目指している。

ソフトウェア面も重要視

たとえそのすべてが成功したとしても、10年後にリリースされるハードウェアは、今日の暗号解読に必要なような複雑なアルゴリズムにはまだ小さすぎるとGambetta氏は言う。つまり、エラー訂正は、古典的なハードウェアでは不可能な計算を実行できるハードウェアが登場する時代の到来を告げるものだが、最終的にそれを使いたいと思うようなすべてのことができるわけではない。つまり、ソフトウェアの開発は、何年もの間、私たちが何を達成できるかを決定する上で非常に重要な要素になるのだ。

IBMは、Qiskitと呼ばれるオープンソースの量子SDKの開発に協力している。このSDKは、プログラマーが実行したいことと、量子コンピューターを制御するハードウェアに直接コマンドを発行する必要性の間に、抽象化のレイヤーを置くものである。本日の発表では、Qiskitの1.0リリースが行われ、APIが安定したことが示された。

これとは別に同社は、Qiskit上で動作するコードを生成できるよう、生成AIコーディングツールを修正した。

ノイズの多いシステムでのエラー緩和や、エラー訂正された量子ビットの数に制約がある場合に、どのような有用なことができるかは完全には明らかになっていない。IBMが年内に2023年プロセッサーの目標を達成するのは喜ばしいことだが、より大きなニュースはそのロードマップだろう。エラー訂正の開発状況について、実用的な形で示されたのは大きな意義を持つ。

Sources