TSMCは、Appleの次世代プロセッサを製造するために使用されている新しいチッププロセスで、リソグラフィツールのトラブルを抱えているようだ。

TSMC CEOであるCC Wei氏は、アナリストに対して、「顧客の需要」にまだ追いついていないと述べているが、これは、ほぼ間違いなくAppleのことを指している。EE Timesは以下のように伝えている:

Taiwan Semiconductor Manufacturing Co. (TSMC)は、トップ顧客であるAppleからの3-nmチップの需要に応えるべく奮闘しています。EE Timesが調査したアナリストによると、同社はツールや歩留まりで苦労しており、世界をリードする技術で大量生産に踏み切るのを妨げているとのことです。

TSMCのCEOであるC.C.Weiは、アナリストとの電話会議で、「当社の3nm技術は、半導体業界で初めて歩留まりの良い大量生産に成功した」と述べた。「お客様のN3に対する需要が当社の供給能力を上回っているため、HPCとスマートフォンの両方のアプリケーションに支えられ、2023年にはN3が完全に活用されると予想しています」。

Appleは2020年12月の時点で、TSMCに3nmプロセッサの全生産量を発注していたと噂されていた。当時、AppleはこのプロセッサーをMac、iPhone、iPad全体で使用すると予想されていた。

製造元のTSMCは、つい最近、3nmプロセスの開発を終えたばかりだった。2月の報道では、TSMCが全生産量をAppleに振り分けることも伝えられていた。

しかし、EE Timesによると、TSMCは、ツールサプライヤーであるASMLからEUVリソグラフィによるマルチパターニングを採用する必要があるため、3nmの導入とランプアップを遅らせているとのことだ。

「EUVマルチパターニングのコストが高いため、EUVのコスト・ベネフィットが魅力的でなくなっている一方で、EUVマルチパターニングの層数を最小限にするために設計ルールを緩めた結果、ダイサイズがかなり大きくなっています。本当の 3nmノードは、より高スループットのEUVシステムであるASMLのNXE:3800Eが2023年後半に利用可能になるまで、スケールしないでしょう」とアナリストのMehdi Hosseini氏は述べている。

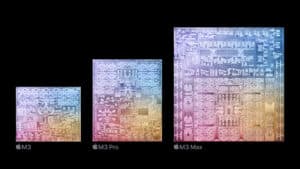

TSMCは、2023年後半にN3ノードでAppleのA17プロセッサとM3プロセッサの増産を開始すると言われている。iPhoneのA17チップでは、TSMCは82層のマスクレイヤーを行い、ダイサイズは100~110mm角の範囲になると見られる。

これは、ウェーハサイクルタイムが4カ月で、ウェーハ1枚当たりの歩留まりが約620チップになることを示している。つまり、M3はダイサイズが135~150mm角で、ウェーハ1枚あたりのチップ数が450個ということになるのだろう。

チップは、数百個のチップからなるウェハーで生産される。Appleは通常、TSMCにウェハー1枚あたりの合意価格を支払うが、現段階ではウェハー上のチップの半分強しか使用できないため、iPhoneメーカーは現在、使用可能なチップ1枚あたりの価格を支払っている。

Arete Researchのシニアアナリスト、Brett Simpson氏は、EE Timesに提供したレポートの中で、Appleは、少なくともN3ランプの最初の3〜4四半期は、歩留まりが70%程度まで上昇するため、標準ウェーハ価格ではなく、既知の良いダイに対してTSMCに支払うだろう、と述べている。

Simpson氏は、「TSMCは、2024年前半にAppleとのN3について、平均販売価格16〜17Kドル程度の通常のウエハベースの価格設定に移行すると考えている」と述べています。「現在、TSMCのA17とM3プロセッサのN3歩留まりは約55%で、TSMCは四半期ごとに約5ポイント以上歩留まりを向上させる予定だと考えています」。

55%という歩留まりは非常に低く聞こえるが、TSMCがまだ新しいプロセスの量産を完成させていない時期には、これが典型的なものであると報告されている。

次の大きなステップは2nmチップで、これは2025年に生産を開始すると予想されている。iPhone 17は、この次期プロセスを採用した最初のデバイスのひとつになると思われる。

Source

コメントを残す