現在、ハイエンドプロセッサーの大半はモノリシック構造だが、微細化の限界が近付き、最先端の製造技術が高価になるにつれて、性能向上を続ける手法の1つとして、マルチチップレットモジュールへの移行が加速している。今後、マルチチップレットのシステムインパッケージ(SiP)の普及が進み、2.5Dおよび3Dチップの高度なパッケージング技術が重要になると予想される中、3D設計の開発を加速・簡略化するために、TSMCは今週、「3DFabric Alliance」を設立した。

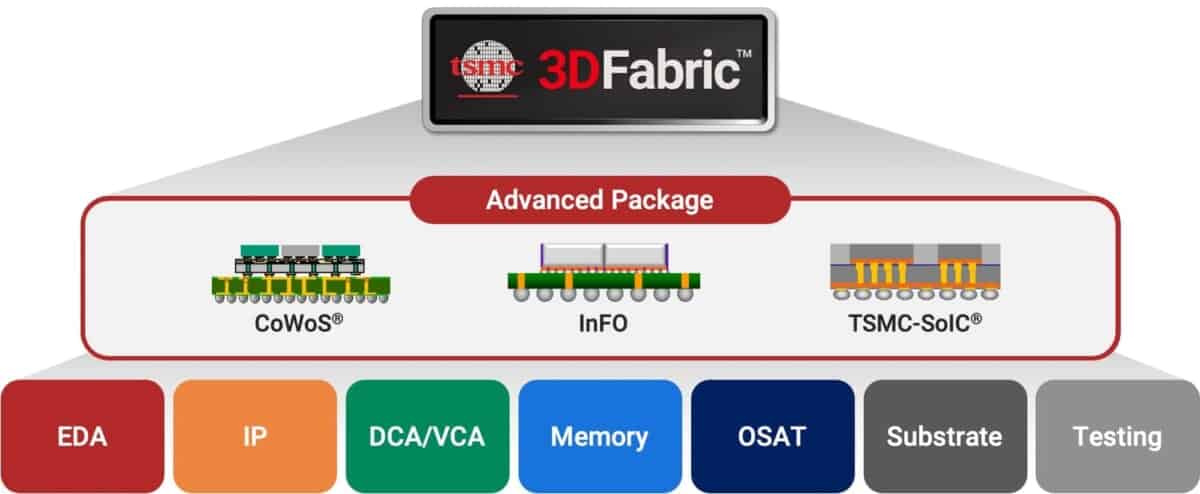

マルチチップレットSiPは、非常に複雑な設計の開発と検証を容易にすることが期待されるが、3Dパッケージは多くの新しい課題をもたらすため、3次元実装に必要な新しい設計フロー、新しい電力供給方法、新しいパッケージング技術、新しいテスト技術など、全く新しい開発手法を必要とする。TSMCの2.5Dおよび3Dパッケージング技術(InFO、CoWoS、SoIC)のメリットを最大限に活用するために、チップ開発業界はチップレットパッケージングに関してエコシステム全体が協調する必要があるとしており、新たな3DFabric Allianceはそれを目指すとしている。

「3Dシリコン積層と高度なパッケージング技術は、チップレベルおよびシステムレベルのイノベーションの新時代への扉を開きますが、設計者が無数の選択肢とアプローチの中から最善の道を切り開くために、広範なエコシステムの協力が必要です」と、TSMCフェロー兼デザイン&テクノロジープラットフォーム担当副社長のL.C. Lu博士は述べている。

TSMCの3DFabric Allianceには、電子設計自動化(EDA)ツールの開発者、知的財産権プロバイダ、受託チップ設計者、メモリメーカー、先端基板メーカー、半導体組立・テスト会社、テスト・検証用機器の製造グループなどが参加している。現在、アライアンスのメンバーは19社だが、時間の経過とともに、新しいメンバーが加わり、拡大していくことが予想される。

TSMCは、アライアンスのリーダーとして、一定の基本ルールと標準を設定する。一方、3DFabricアライアンスのメンバーは、TSMCの3DFabric技術の仕様の一部を共同で定義、開発し、TSMCの3DFabricロードマップと仕様にいち早くアクセスし、ファウンドリの計画だけでなくアライアンスの他のメンバーの計画とも整合させ、新しいパッケージ方法に対応するソリューションを設計、最適化できるようになる。

最終的には、TSMCは、3DFabricアライアンスのメンバーが、2.5Dおよび3Dパッケージを使用するマルチチップSiPの迅速な開発および検証を可能にする、互換性と相互運用性のあるソリューションを顧客に提供できるようにしたいと考えている。

例えば、認定されたEDAツールとフローで設計エコシステムを統一するために、TSMCは3Dblox規格を開発した。3Dbloxは、物理的実装、消費電力、放熱、エレクトロマイグレーションIRドロップ(EMIR)、タイミング/物理的検証など、2.5Dおよび3Dパッケージング手法(チップレットやインターフェース定義など)を採用したマルチチップレットデバイス構築のさまざまな側面をカバーしている。

「TSMCとエコシステム・パートナーのリーダーシップにより、3DDFabricアライアンスは、お客様の設計において3D ICのパワーを引き出すための簡単で柔軟な方法を提供します。当社の 3DFabric テクノロジで作成できるイノベーションを見るのが待ちきれません。 」とLu博士は付け加えた。

最終的にTSMCは、この提携により、特に外部IP/設計への依存度が高い中小企業にとって、より高度なチップの開発プロセスが大幅に簡素化・合理化されることを想定している。例えば、ある企業がロジックチップレットを積層し、HBM3ベースのメモリサブシステムに接続したSiPを開発したい場合、Ansys Cadence、Synopsys、SiemensのEDAソフトウェアによって互換チップレットを設計し、IPプロバイダによって設計者がまだ持っていないブロックを販売し、TSMCがシリコンを生産し、メモリメーカーが互換性のあるHBM3 KGSD(既知の良好な積層ダイ)を提供して、Ase Technologyによってすべてを組み立てることができるようになる。一方、自社にエンジニアを持たない企業は、Alchip社やGUC社を通じてSiP全体(または個々のチップレット)の設計を発注し、その後、必要に応じて製品を更新することができる。SiPは3DFabricと3Dbloxの標準に従って構築されるため、すべてを設計し直す必要はない。

3Dbloxは現在、4つの主要なEDAデベロッパーによってサポートされている。最終的には、必要に応じてアライアンスの全メンバーによってサポートされる予定だ。

AMDやNVIDIAのような大企業は、独自のIP、相互接続、パッケージング技術を開発する傾向があるが、マルチチップレットSiPは、複雑なチップレット型プロセッサの開発を中小企業にも可能にすることが期待される。これらの企業にとって、標準的なサードパーティIP、迅速な市場投入、適切な統合は成功の鍵であり、3DFabricアライアンスとそれがもたらすものは不可欠なものとなるだろう。

コメントを残す