Samsungが半導体業界で1つのマイルストーンを達成した。同社は本日、世界初の3nm GAAチップの生産開始を発表したのだ。これにより、今後のモバイルデバイスを初めとする様々な製品に大きなメリットがもたらされることになる。そして今後の性能・歩留まり如何によっては、半導体業界の勢力図が塗り替えられる可能性も秘めている。

Samsung 3nm MBCFETでは、PPAで大きなメリットが得られる

Samsung Electronicsの社長兼ファウンドリビジネス責任者であるSiyoung Choi博士は、この新しいアーキテクチャを自信を持って発表している。

Samsungは、業界初の High-Kメタルゲート、FinFET、EUV など、次世代技術の製造への適用においてリーダーシップを発揮し続け、急成長を遂げてきました。私たちは、世界初の3nmプロセスであるMBCFET™で、このリーダーシップを継続することを目指しています。今後も、競争力のある技術開発に積極的に取り組み、技術の成熟化を促進するプロセスを構築していきます。

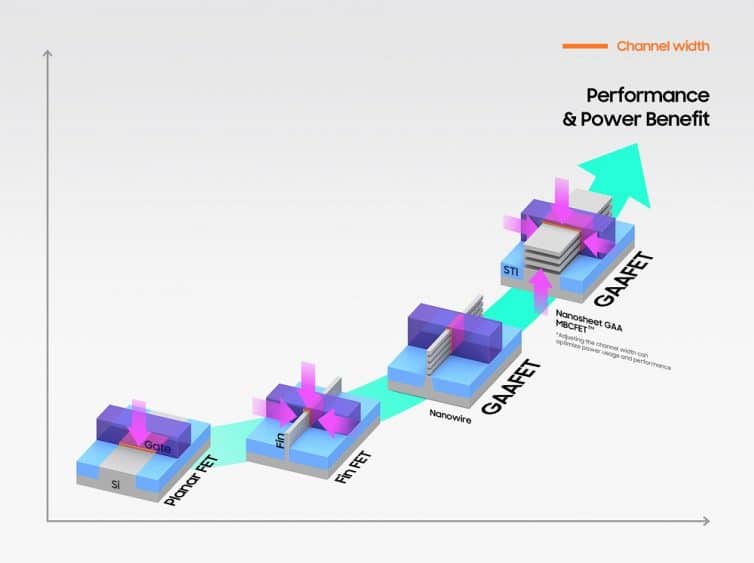

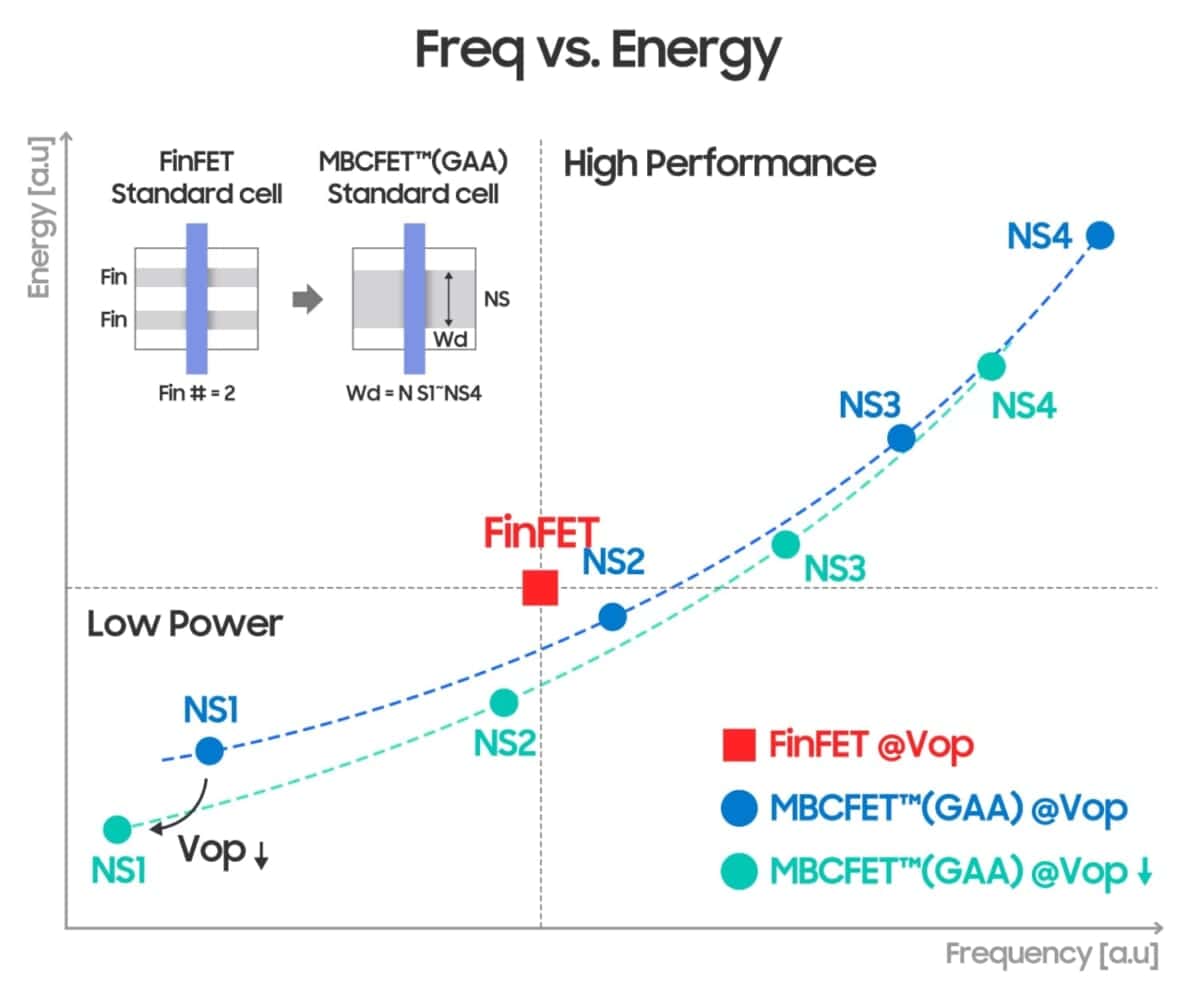

Samsungは、3nmのGAAチップを生産するために、独自技術でチャネル幅の広いナノシートを使用する別の方法を用いている。同社はこれを、MBCFET(Multi-Bridge-Channel-FET)と名付けているが、この手法により、チャネル幅の狭いナノワイヤを用いたGAAよりも高い性能とエネルギー効率の向上が可能となる。Samsungによると、GAAは設計の柔軟性を最適化し、PPA(Power, Performance, and Area)において大きなメリットが得られるとのことだ。

ナノワイヤ方式によるGAAの採用については、SamsungのみならずIntel、TSMCも今後採用する予定だが、今回Samsungが一歩先んじた形となる。

5nmプロセスと比較した場合、Samsungは3nm GAAによって、消費電力を最大45%削減し、性能を23%向上させ、面積を16%削減することができると述べている。ただ、4nmプロセスと比較した場合の改善点について述べていないところに少し疑問も生じるが、さらに興味深い事には、プレスリリースでは第2世代の3nm GAA製造プロセスについても進行していることが述べられている。

その第2世代プロセスでは、5nmプロセスに比べて消費電力を最大50%削減し、性能を30%向上させ、面積を35%削減することが可能になると、圧倒的な数字が並んでいるが、Samsungは、3nm GAAの歩留まりについてはコメントしていない。ただ、以前に流れた報道によると、状況は悪いようだ。どうやら、4nmが歩留まり率35%だったのに対して、3nm GAAでは10~20%の間と言われている。

Qualcommは、TSMCが3nmプロセスの歩留まり問題に直面することを想定して、Samsungの3nm GAAノードを予約したと言われている。Samsungは特別にその最先端技術をQualcommに提供し、Qualcommが満足すれば、将来のSnapdragonチップセットの受注がTSMCからSamsungに切り替わる可能性もあるようだ。

ただし、一部報道ではTSMCの3nmプロセスの歩留まりは想定よりも良いとの話も出てきている。

TSMCについては、今年8月には3nmチップの試験生産を開始し、今年後半に3nmチップの量産を開始する予定であり、Appleは幅広いMacに向けた次期M2 ProおよびM2 Max SoCで優先的に最先端のラインを割り当てられるようだ。

Qualcommが最新のフラグシップSnapdragonでSamsungからTSMCに生産を切り替えた原因となる諸問題が解決され、安定した供給、性能が実現し、半導体業界にとってより良い競争が生まれることを願いたい。

コメントを残す