投資銀行のMorgan Stanleyが、台湾積体電路製造公司(TSMC)は、次世代チップ製造技術について、“素晴らしい歩留まり”を得られており、3nmチップの製造が早まる可能性があることを報告している。

WCCFtech : TSMC Exceeds 3nm Yield Expectations & Production Can Start Sooner Than Planned

RetiredEngineer®(@chiakokhua) : Twitterへの投稿

- TSMC「N3ノード」のアップグレード版「N3e」の歩留まりが想定以上に良好

- 「N3e」の量産は前倒しされ、2023年第2四半期までに開始される可能性

TSMCによる「N3e」の製産が早まる可能性

「N3e」と名付けられたこの製造技術は、TSMCのN3ノードをアップグレードしたもので、一部のトランジスタの寸法を3ナノメートルまで縮小することが期待されるものだ。

このレポートの断片は、Twitterにて、RetiredEngineer®(@chiakokhua)名乗るユーザーによって投稿された。彼はMorgan Stanleyが装置ベンダーに確認したことを引用し、TSMCが早ければ2022年3月末までにN3eノードの設計パラメータを「凍結」する可能性を示唆している。これは、同プロセスの歩留まりが予想以上に良いためで、チップノードが量産に入る前の最終段階の1つである同プロセスの量産が、来年の第2四半期までに始まる可能性を示している。

N3eの生産歩留まりが向上、スケジュールを引き寄せ中。装置ベンダーに確認したところ、TSMCはN3eプロセスフローの凍結を早め、今年3月末までに行う可能性があるとのことです。これは、N3eの量産開始が、当初予定の2023年第3四半期からから4分の1程度前倒しで2023年第2四半期になる可能性があることを意味します。N3eの試作歩留まりは、N3bよりはるかに高くなっています。当社のチェックでは、EUV層を4層削減することで、N3eのロジック密度はオリジナルのN3より8%程度低くなっていますが、それでも5nmより60%高い密度を保っています。これらのことから、N3eはTSMCにとって、コストとタイミングの面で競争力のあるノードであると言えます。

RetiredEngeneerによるTwitterへの投稿

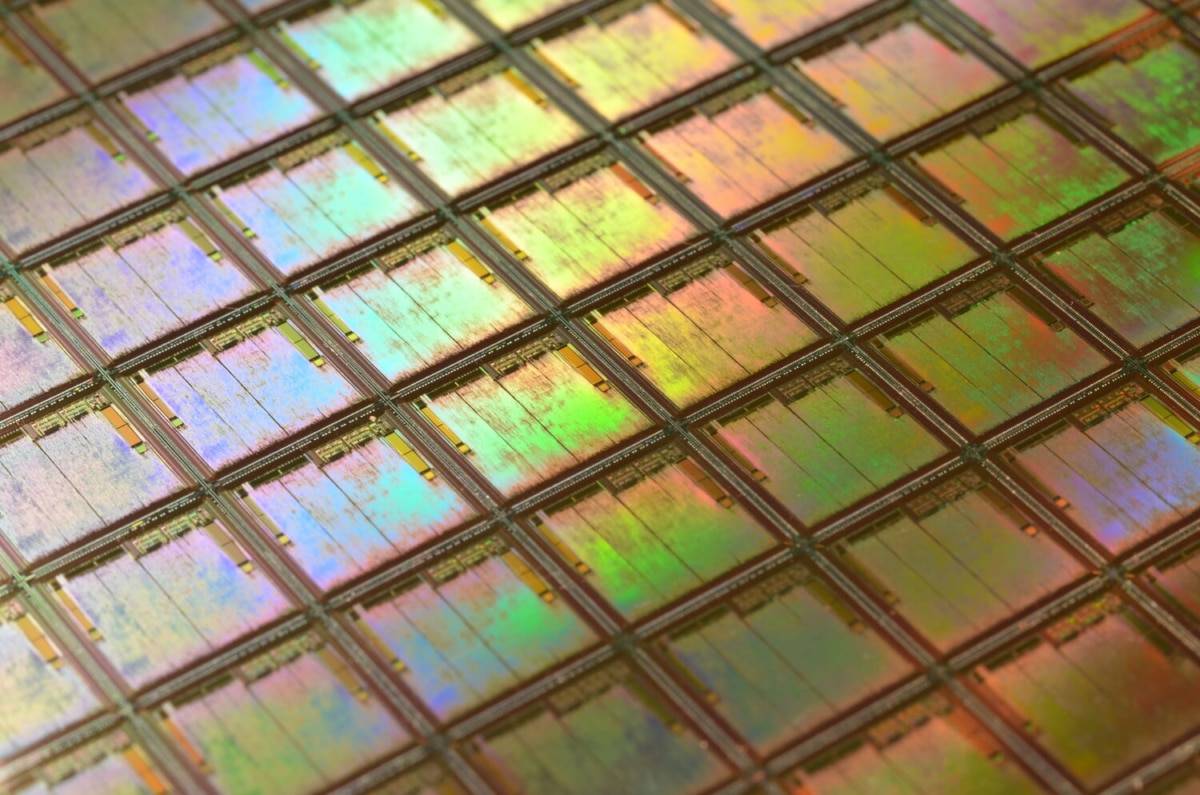

ただ一方で、台湾の情報筋が、TSMCが3nmの歩留まりで問題に直面していると推測していた事も一応留意しておく必要がある。半導体業界では、プロセスの歩留まりは、単一のウェハーの品質管理チェックに合格するチップの数として定義され、歩留まり率が高いほど、プロセスは成熟したと見なされる。TSMCなどのFabは、顧客との関係を深め、製品の品質を向上させるため、この工程を完成させるのに時間がかかることがよくある。

また、歩留まりが悪いためにTSMCによって一時的な対策として導入されたと以前に推測されていたN3bノードの存在についても言及している。以前のレポートでは、TSMCの顧客は、歩留まりの欠陥が疑われるため、比較的成熟した5nmノードを使用することを選択したと推測していたが、これが依然として当てはまるかどうかは不明だ。

昨年共有された元のN3ノードに関するTSMCの公式の数字は、このプロセスの密度が5nmプロセスよりも70%高いことを示している。Morgan Stanleyの「5nmプロセスに比べて密度が60%の増加、および第1世代のN3に比べて8%の減少」という数字は、チップメーカーが共有する見積もりと一致している。

N3eノードは、昨年の2021年第3四半期の投資家向け電話で、TSMCの最高経営責任者であるCC Wei博士が、「パフォーマンス、電力、歩留まりが向上した、製造プロセスの改善を特徴としています」と概説している。Fabは現在、最新のチップ製造技術の開発で米国のチップ大手Intel Corporationと競合しており、この面では、生産を合理化し、市場の需要を満たすことができる一方で、両方が新しいマシンを取得し、トランジスタサイズに関する競争を行う可能性がある。

コメントを残す