AMDの次期グラフィックスカードとされる、「Radeon RX 7000シリーズ」だが、この中でフラッグシップSKUに搭載されると言われる「Navi 31チップ」などのAMDの最初および今後のRDNA 3 GPUは、最大7つのチップレットを搭載すると噂されている。

Greymon55 : Twitterへの投稿

- AMDはRyzen CPUで採用していた「チップレットテクノロジー」をGPUでも大いに活用し、性能向上を目指している

- 次期フラグシップRadeonに搭載されるGPU「Navi 31」には、最大7つのチップレットが搭載される可能性

- 各ダイはTSMCの5nm及び6nmプロセスで製造される

AMDはCPUで培ったチップレットテクノロジーをGPUにも活用か

AMDはRyzen CPUで培ったチップレットテクノロジーを、Radeon GPUでも活用するようだ。RDNA 3の上位GPUの設計手法としてMCM(Multi-Chip-Module)を採用することについては、以前からいくつかの噂や憶測が流れていた。Greymon55氏の最新のツイートでは、フラッグシップGPUの「Navi 31」が7個ものチップレットを搭載できることをリークしている。

AMD RDNA 3 GPUのラインナップは、MCMとモノリシックの両方を採用するとされ、TSMCの6nmと5nmのプロセスノードを利用する予定とのことだ。

フラッグシップモデルとなる「Navi 31 GPU」は、5nmプロセスノードベースの2つのGCDと、6nmプロセスノードベースの4つのMCD、そして同じく6nmプロセスノードベースのシングルIOダイを搭載と、盛りだくさんになるようだ。GCDはGraphics Compute Dieで、インターポーザーに搭載されるメインGPUチップとなり、MCDはMemory Complex DieまたはMulti Cache Dieと呼ばれ、Infinity Cacheと関連するメモリコントローラを搭載する。IOダイは、メディアエンジンとその他のIOレイヤーで構成されるチップになる予定だ。MCDがインターポーザーの上に搭載されるのか(3D Stacking)、それとも別個に搭載されるのかについては、まだハッキリとした情報は出ていない。

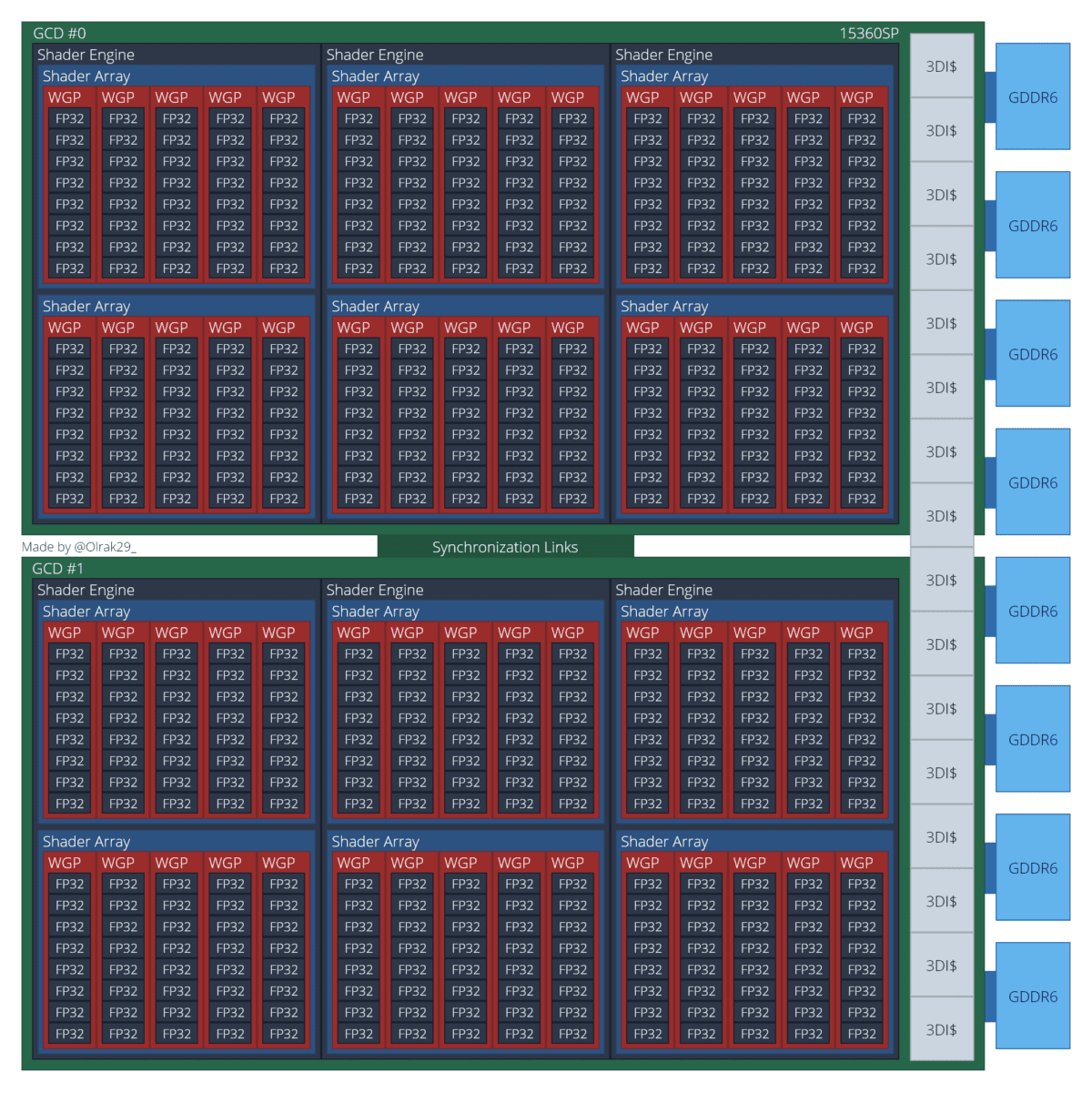

今回ブロック図で紹介するNavi 31のGPU構成は、2つのGCD(Graphics Core Die)と1つのMCD(Multi-Cache Die)を搭載している。各GCDは3基のShader Engine(合計6基)を持ち、各Shader Engineは2基のShader Array(SEあたり2基/GCDあたり6基/合計12基)を持つ。各Shader Arrayは5つのWGP(SEあたり10個/GCDあたり30個/合計60個)で構成され、各WGPには32個のALUを持つSIMD32ユニット(SAあたり40個/SEあたり80個/GCDあたり240個/合計480個)を8個搭載する。これらのSIMD32ユニットを組み合わせ、1GCDあたり7,680コア、合計15,360コアを構成している。

Navi 31(RDNA 3)のMCDは、次世代インターコネクト「Infinity Fabric」でデュアルGCDにリンクされ、256~512MBのInfinity Cacheを搭載する予定だ。また、各GPUは、4本のメモリコネクトリンク(32-bit)を搭載すると思われる。つまり、256-bitのバスインターフェイスに対して、合計8個の32-bitメモリコントローラを搭載することになる。

これまで、次期RDNA 3 GPUは、ラスタライズ性能の点でNVIDIAの提供するものを凌駕するという噂がいくつかあった。AMDは、Radeon RXグラフィックスカードのラインナップで、最初のMCM搭載GPUを提供することで優位に立つ考えだろう。しかし、同時にNVIDIAは、Ampere GPUの3倍以上の性能向上を実現するMCM GPUラインナップに速やかに移行すると予想されている。

コメントを残す