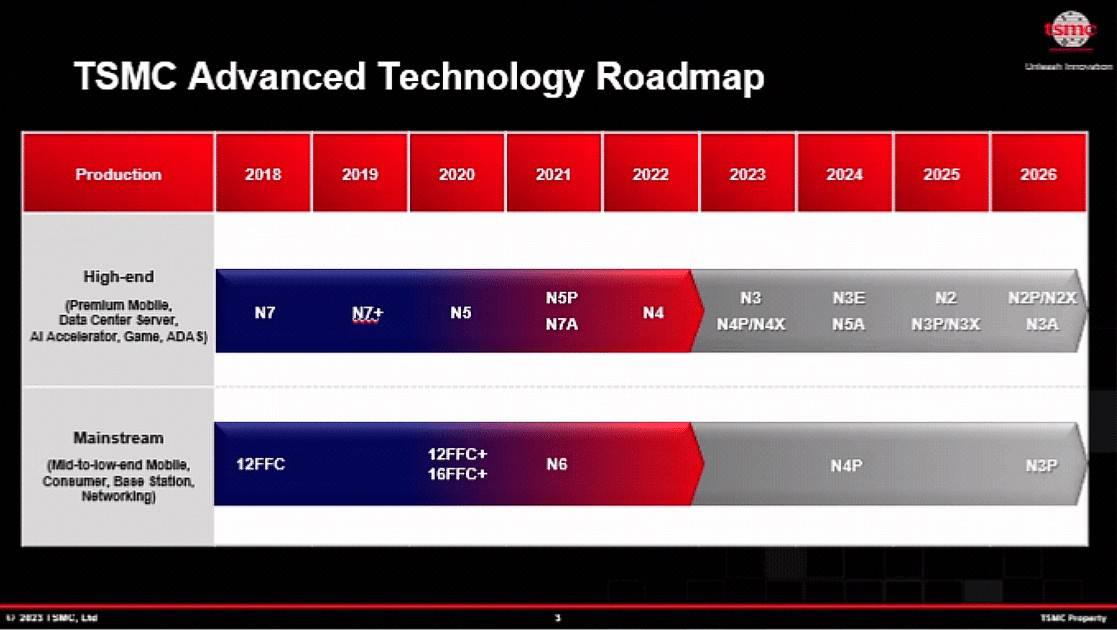

TSMCは、2023 North American Technology Symposiumにおいて、2nmプロセスノード計画に関するいくつかの新しい発表とともに、N3ファミリープロセス技術の進捗状況とロードマップの最新情報を発表した。TSMCのFinFETトランジスタに基づくTSMCの最終的な高性能ノードとして、N3は長年にわたって存続し、N3Eの性能を向上させる光シュリンクであるN3Pや、高リークと電力を許容するHPCアプリケーション向けの性能重視のN3Xなど、複数のバージョンを含む予定だ。

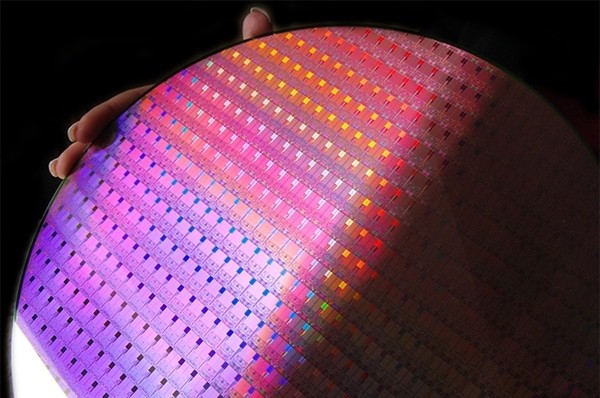

TSMCのN3(N3Bとも呼ばれる)プロセス技術による量産はすでに始まっているが、このノードは最大25層で極端紫外線リソグラフィーを使用し、EUVダブルパターニングも使用できるため、使用するには特に高価なノードとなっている。そのため、TSMCは、19層までEUVを使用でき、EUVのダブルパターニングを使用せず、プロセスウィンドウが広く、歩留まりが良いN3Eを顧客の大半が使用すると見込んでいる。2023年下半期に大量生産に使用されるN3Eは、TSMCのさらなる3nmの進化のベースにもなる予定だ。

TSMCのN3に関するロードマップの大きな更新は、N3Pとその高性能版であるN3Xに関するものだ。TSMCが明らかにしたように、N3PはN3Eを光学的に縮小したもので、N3Eの設計ルールとの互換性を維持しながら、N3Eと比較して性能向上、消費電力低減、トランジスタ密度向上を実現する。一方、N3Xは、3nmクラスの高密度化で極めて高い性能を実現し、高性能CPUやその他のプロセッサに高いクロックスピードを提供する。

また、TSMCは、N2ファミリーを拡張し、裏面パワーレールを搭載するN2Pを計画しており、性能の向上、消費電力の削減、トランジスタ密度の向上を約束する。さらに、TSMCは、最高の性能と高電圧への対応を実現するために設計されたノードであるN2Xを計画している。

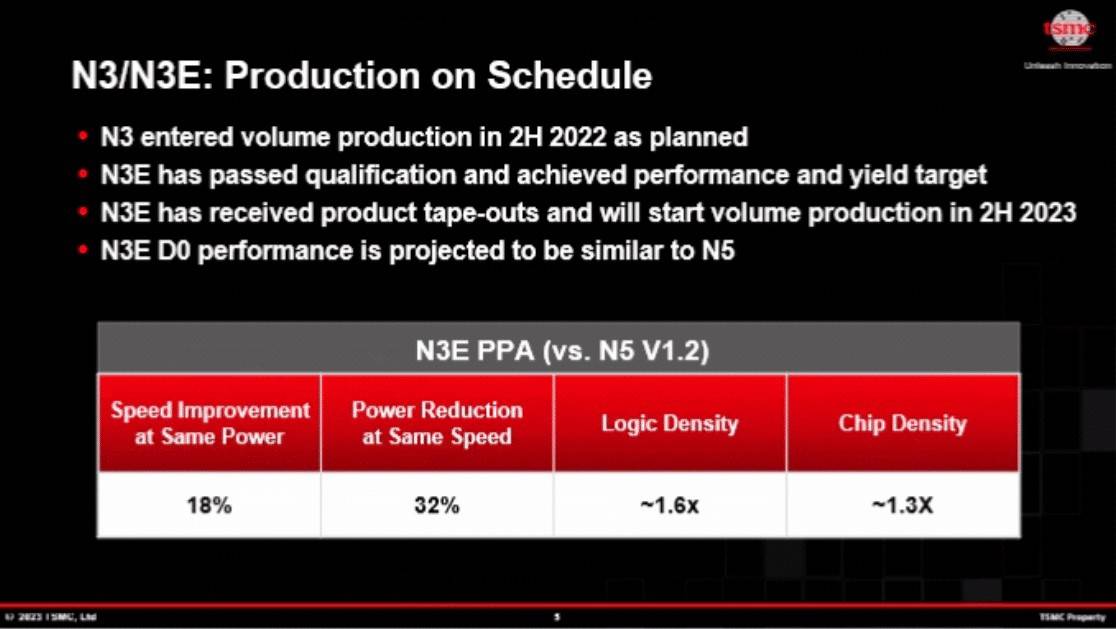

N3E:多くの顧客にマッチする

TSMCのN3(3nmクラス)プロセス技術ファミリーは、ベースラインN3(別名N3B)、コストを削減した緩和型N3E、性能とチップ密度を強化したN3P、電圧耐性を高めたN3Xなどのバリエーションで構成されている。昨年は、トランジスタ密度を最大化するN3Sについても言及したが、今年はこのノードについてはまだ言及されていない。

TSMCの標準のN3ノードは、最大25層のEUV層を備えており、TSMCはその一部にEUVダブルパターニングを使用して、N5よりも高いロジックおよびSRAMトランジスタ密度を実現している。EUV工程は一般的に高価であり、EUVダブルパターニングはそのコストをさらに上昇させるため、この製造工程は、必要な高額費用をあまり気にしない一握りの顧客によってのみ使用されると予想される。

TSMCによると、3nmクラスのプロセスに関心を持つTSMCの顧客の大半は、ゆったりとしたN3Eノードを使用する見込みで、予定通り、性能目標を達成しているとのことだ。N3Eは、最大19層のEUV層を使用し、EUVダブルパターニングに全く依存しないため、その複雑さとコストを削減することが出来る。しかし、N3EはN3よりもロジック密度が低く、SRAMセルサイズもTSMCのN5ノードと同じであるため、密度や面積の向上を目指す顧客にとってはやや魅力に欠ける。全体として、N3Eは、チップ製造における2つの重要な指標である、より広いプロセスウィンドウとより良い歩留まりを約束する。

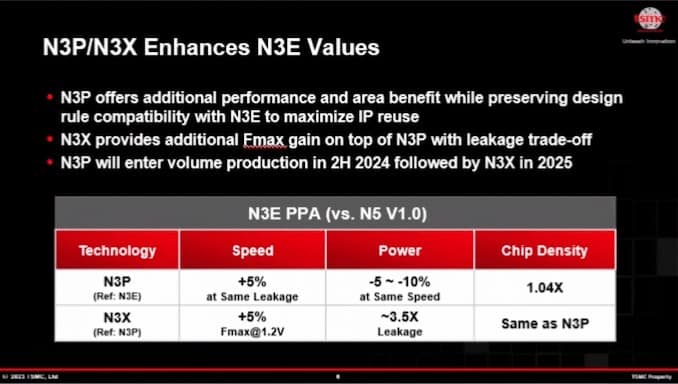

N3P:高性能化、高トランジスタ密度化

N3Eに続き、TSMCはN3PでN3ファミリーのトランジスタ密度の最適化を継続し、N3Eをベースにトランジスタの特性を改善する。このプロセス・ノードの改良により、チップ設計者は、同じリーク電流で性能を5%向上させるか、同じクロックで電力を5~10%削減することが出来る様になる。また、TSMCがロジック50%、SRAM30%、アナログ回路20%で構成されるチップと定義する「ミックスド」チップ設計では、この新ノードによってトランジスタ密度が4%向上する。

TSMCは、N3Pに関する議論の一環として、密度の向上はスキャナの光学性能を調整することで実現したことを強調した。つまり、ここではTSMCがあらゆるタイプのチップ構造をシュリンクできる可能性が高く、N3PはSRAMを多用する設計にとって魅力的なノードになると考えられる。

TSMCによると、「N3Pは、N3Eに比べ5%以上性能が向上しており、2%の光収縮を実現し、トランジスタ密度を1.04倍に高めている」とのことだ。

N3PはN3Eを光学的に縮小したものであるため、N3Eのデザイン・ルールが維持され、チップ設計者はN3EのIPを新しいノードで迅速に再利用することが可能になる。そのため、CadenceやSynopsisなどのIPデザイン・ハウスは、このプロセス・テクノロジー向けにさまざまなIPを提供し、既存のN3Eとの前方互換性のメリットを享受することが期待される。TSMCは、N3Pは2024年後半に生産準備が整うと述べている。

N3X:最高のパフォーマンスと密度

最後に、CPUやGPUなどの高性能コンピューティング・アプリケーションの開発者向けに、TSMCは過去数世代にわたり、高電圧でパフォーマンスに特化したXファミリーのノードを提供してきた。昨年のイベントで発表されたように、N3ファミリーは、N3Xノードという適切な名前の、独自のXバリエーションを持つことになる。

N3Eと比較して、N3XはN3Pと比較して少なくとも5%高いクロックスピードを提供すると予測されている。これは、ノードの高電圧耐性を向上させることで達成され、チップ設計者は、全体的なリーク量が増える代わりにクロックスピードを上げることが出来る。

TSMCは、N3Xが(少なくとも)1.2Vの電圧をサポートすると主張しているが、これは3nmクラスの製造プロセスとしてはかなり極端な電圧である。TSMCは、よりバランスのとれたN3Pノードと比較して、リーク電力が250%増加すると予測しているため、リークコストは非常に大きくなる。このことは、N3XがHPCクラスのプロセッサにしか使えない理由と、チップ設計者が最も強力な(そして電力消費の多い)チップを抑制するために細心の注意を払う必要があることを明確に示している。

トランジスタ密度については、N3XはN3Pと同じ密度を提供する予定だ。TSMCは、N3PとN3Eとのデザインルールの互換性も維持するかどうかについてはコメントしていないので、最終的にどうなるのかが注目される。

TSMCの現在のロードマップにおける最後のN3ファミリーノードであるN3Xは、2025年に生産準備が整うとしている。

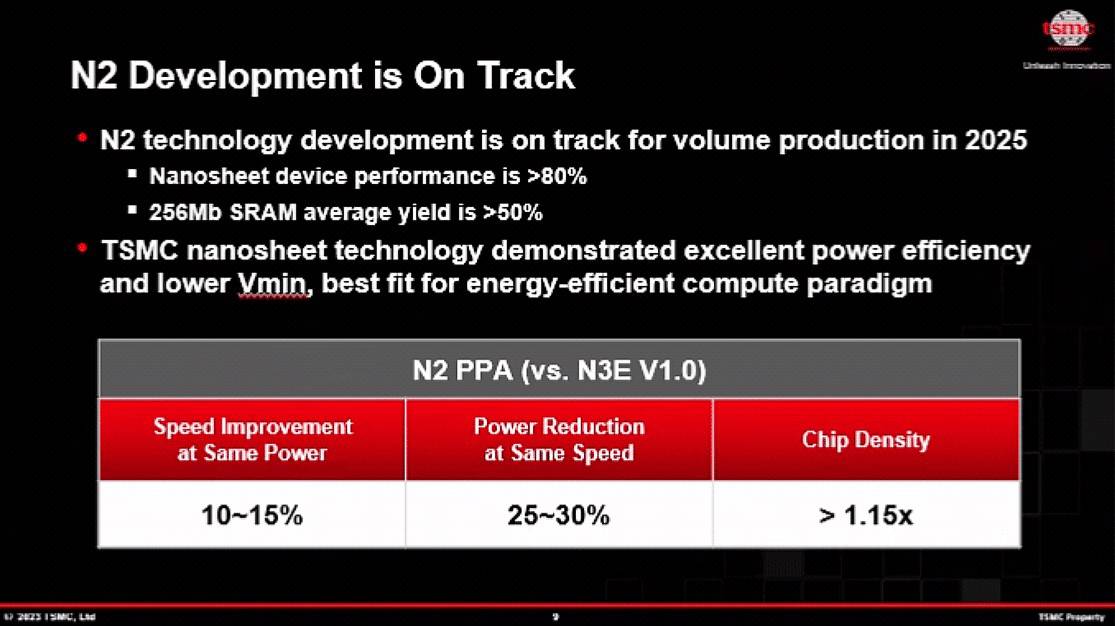

N2:2025年に登場する初のGAA世代

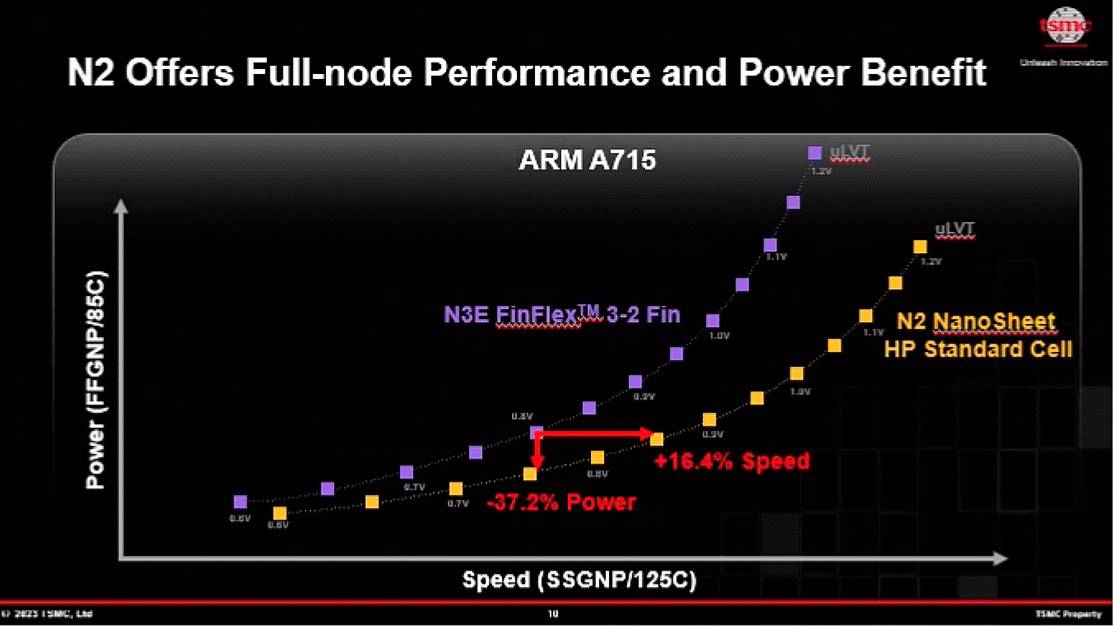

TSMC のオリジナル N2 プロセス技術は、2025 年に大量生産を開始する予定で、ゲートオールアラウンド (GAA) ナノシートトランジスタを導入している。N3Eと比較した場合、この新しいノードでは、同じ電力とトランジスタ数で性能を10%から15%向上させるか、同じ周波数と複雑さを維持しながら消費電力を25%から30%低下させるとのことだ。スケーリングに関しては、TSMCは詳細な数字の提示を控えているが、新しい製造技術によってチップ密度を15%向上させることができると述べている。この言葉は、ロジック50%、SRAM30%、アナログ回路20%を含む仮想のICを反映しているので、あいまいな表現になっている。

TSMCのN2の進捗は、計画通りのようだ。TSMCはシンポジウムで、ナノシートGAAトランジスタの性能が目標仕様の80%以上に達したこと、256Mb SRAMテストICの平均歩留まりが50%を超えたことを発表した。

N2P:バックサイドパワーデリバリーによる性能効率向上

N2 は N3E に比べて目に見える利点があるが、その後継である N2P はさらに素晴らしいものになることが期待される。TSMCの第2世代2nm級プロセスには、バックサイド・パワー・デリバリ・ネットワーク(PDN)が組み込まれており、トランジスタの性能向上、消費電力の低減、トランジスタ密度の向上、チップ内のデータ線と電源線の干渉リスクを排除するよう設計されている。

バックサイドパワーデリバリーは、近年、最も重要な技術革新の一つである。パワーレールをウェハの裏側に移動させることで、バックサイドパワーデリバリーはI/Oとパワー配線を分離し、BEOLで発生する高抵抗の問題を軽減することが出来るものだ。

TSMCは、N2PのN2に対する性能、電力、面積(PPA)のメリットについて具体的な数値を提示していないが、一部のアナリストは、バックサイドPDNによって、消費電力が1桁減少し、トランジスタ密度が2桁増加する可能性があると述べている。TSMCはN2Pに対してさらなる最適化を行う可能性があることを念頭に置き、この技術が性能効率とトランジスタ密度の両面でN2やN3よりも大幅に進歩することを期待している。

TSMCは、N2Pが2026年に大量生産(HVM)できるようになると予想しており、このノードで作られた実際のチップは2027年に出荷されると予想される。Intelが約束を果たし、2024年に20A生産技術(RibbonFET GAAトランジスタとPowerViaバックサイドPDNの両方を採用)で作られた最初のチップを出荷すると仮定すると、バックサイドパワーレールでTSMCより2~3年先に進むことになる。

N2X:高電圧で極限まで性能を引き出す

TSMC は、ハイエンドのデータセンター向け CPU などのハイパフォーマンス・コンピューティング (HPC) アプリケーション向けに調整された製造プロセスである N2X を開発しています。一般に、これらのチップは電力を消費するため、ピーク時の要求に応じてクロックを上げる機能が必要だ。つまり、高電圧・高電流に対応する必要がある。このノードが利用可能になるのは早くても2026年であるため、TSMCは、N2、N2P、N3Xに対する性能強化の概要は明らかにしていない。一方、最近の生産技術と同様に、最大の性能と効率は、ファウンドリとIP開発者の間で広範な設計技術共同最適化(DTCO)を行うことによってのみ達成できる。

Source

コメントを残す