最先端半導体の製造にはますます巨額の費用がかかる。ツールはより複雑になり、必要な人材もより高価になるため、2nmの開発・生産プロセス全体のコストは上昇するだろう。1つの救いは、プロセスを合理化し、コスト削減に役立つAI対応のEDAツールかもしれない。

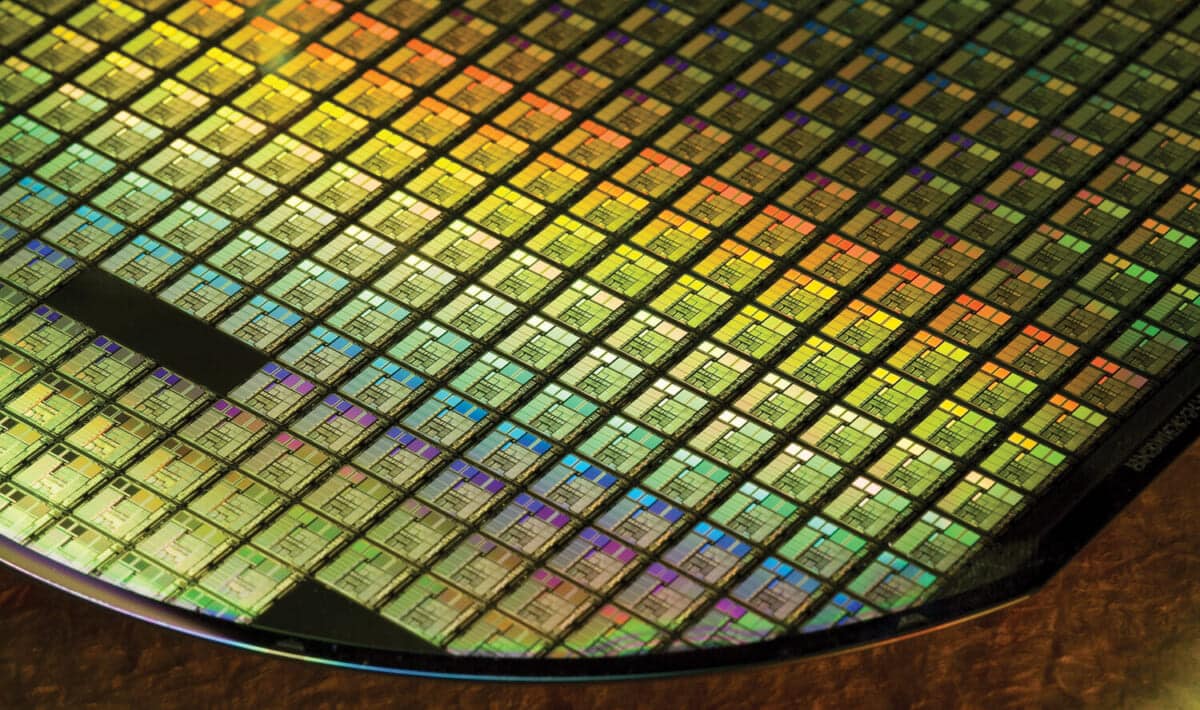

コンサルティング会社IBSによると、月産5万枚のウェハースタート(WSPM)能力を持つ2nm対応半導体製造工場の構築には、約280億ドルかかるという。これは3nm工場のコスト200億ドルより80億ドルも高く、業界が次世代チップに移行するにつれて、企業が期待できる費用が指数関数的に増加することを示す一例である。

正確には、2nmチップのコストは3nmプロセッサーに比べて約50%上昇するとIBSは述べている。つまり、Appleのような企業は、TSMCのN2ファブリケーション・プロセスが数年後に導入された場合、300mmウェハー1枚を加工するのに3万ドルを費やさなければならないことになる。しかし、この数字には多少の余裕もあり、チップの予想されるコスト高を下げられる可能性がある。

実際、半導体企業が取ることのできるアプローチは数多くあり、工場建設前、建設中、操業中に下すことのできる設計上の決断の数々によって、工場の最終的なコストは大きく変わってくる。

確かに、チップ開発にかかる費用は馬鹿にならない。ソフトウェア開発だけで3億1,400万ドル、検証で1億5,400万ドルかかるとIBSの数字は示している。また、2nmノードでチップを設計するには専門的な人材が必要だが、それも不足している。さらに、フォトリソグラフィ(チップ表面のパターンを作成するためのプロセス)の使用量も増加している。

チップ上のフィーチャーが小さくなればなるほど、フォトリソグラフィ工程はより精密になる必要があるため、工程で使用される装置や材料のコストが上昇する。では、何が2nmプロセス対応工場のコストを押し上げ、280億ドルもの巨額の費用を必要としているのだろうか?3nmプロセス対応工場80億ドルのコスト差のほとんどは、50,000WSPMの生産能力を維持するために必要なEUVリソグラフィ装置の台数の増加だ。

しかし、IBS社でさえ、このような数字の裏にはニュアンスの違いがあり、チップ設計の状況が進化していることを認めている。IBSは、大規模な2nmチップをゼロから製造するのに7億2,500万ドルかかると見積もっている。しかし、それは既存の知的財産を持たない企業によるものであり、現実には多くの半導体企業、特に新興企業がより効率的な戦略を追求している。

IBSはまた、複雑な設計プロセスを自動化し、チップ性能を最適化することでプロセスを合理化し、コストを削減するAI対応EDAツールの役割は、チップ設計においてますます重要になってきているとも指摘している。

とはいえ、2nmの製造コストとウェハ・コストを非常に大まかに見積もっても、2nmノードで製造されるチップは、3nmクラスのプロセス技術で製造されるプロセッサーよりも高価になることは間違いない。AppleのiPhone向けチップ等のスマートフォンのプロセッサーは、先端パッケージング・コストがまだかなり高いため、しばらくはモノリシック設計が維持される可能性が高い。

Sources

コメントを残す