Samsungが今後度入予定のSF1.4(1.4nmクラス)のプロセス技術について、Samsung Foundryの副社長Jeong Gi-Tae氏がThe Elecのインタビューに応じ、いくつかの情報を明らかにしているようだ。

Samsungの1.4nmプロセスでは、現在最先端プロセスで導入しているナノシートの数を3枚から4枚に増加させるとのことである。この変更により、チップの性能と消費電力において大きな利点が期待されるとのことだ。

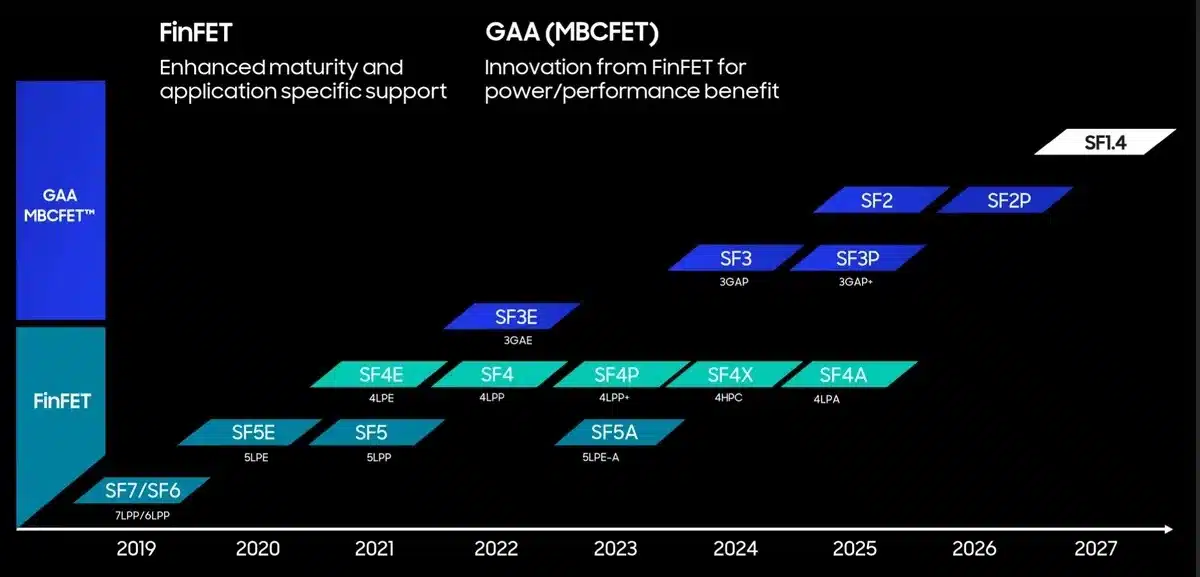

Samsungは、2022年半ばにSF3E(別名3nmクラスのGate All Around Earty: 3GAE)として、GAAナノシートトランジスターを用いたプロセス技術を業界で初めて導入した。

来年、Samsungはより多くの用途に適用可能なSF3技術を導入する計画だ。2025年には、データセンターのCPUとGPUを対象とした性能強化版のSF3P技術をローンチする予定もある。同年には、GAAトランジスターに加えて、裏面電力供給機能を備えたSF2(2nmクラス)の製造プロセスも導入される予定だ。

その後の最も大きな変更は、2027年に予定されているSF1.4技術の導入で、ナノシートの数が3枚から4枚に増加することだ。ナノシートの数を増やすことで、トランジスターを通る電流が増加し、スイッチング能力と動作速度が向上する。さらに、電流の流れをより良く制御できるため、リーク電流が減少し、消費電力が削減される。このような改良により、トランジスターが発生する熱も減少し、電力効率が向上するとされている。

IntelとTSMCも、それぞれ2024年と2025年にGAAトランジスターを使用した20AおよびN2(2nmクラス)のプロセス技術を導入する予定であるが、その時点でSamsungはすでにGAAトランジスターに関する豊富な経験を有している可能性が高い。

Sources

コメントを残す