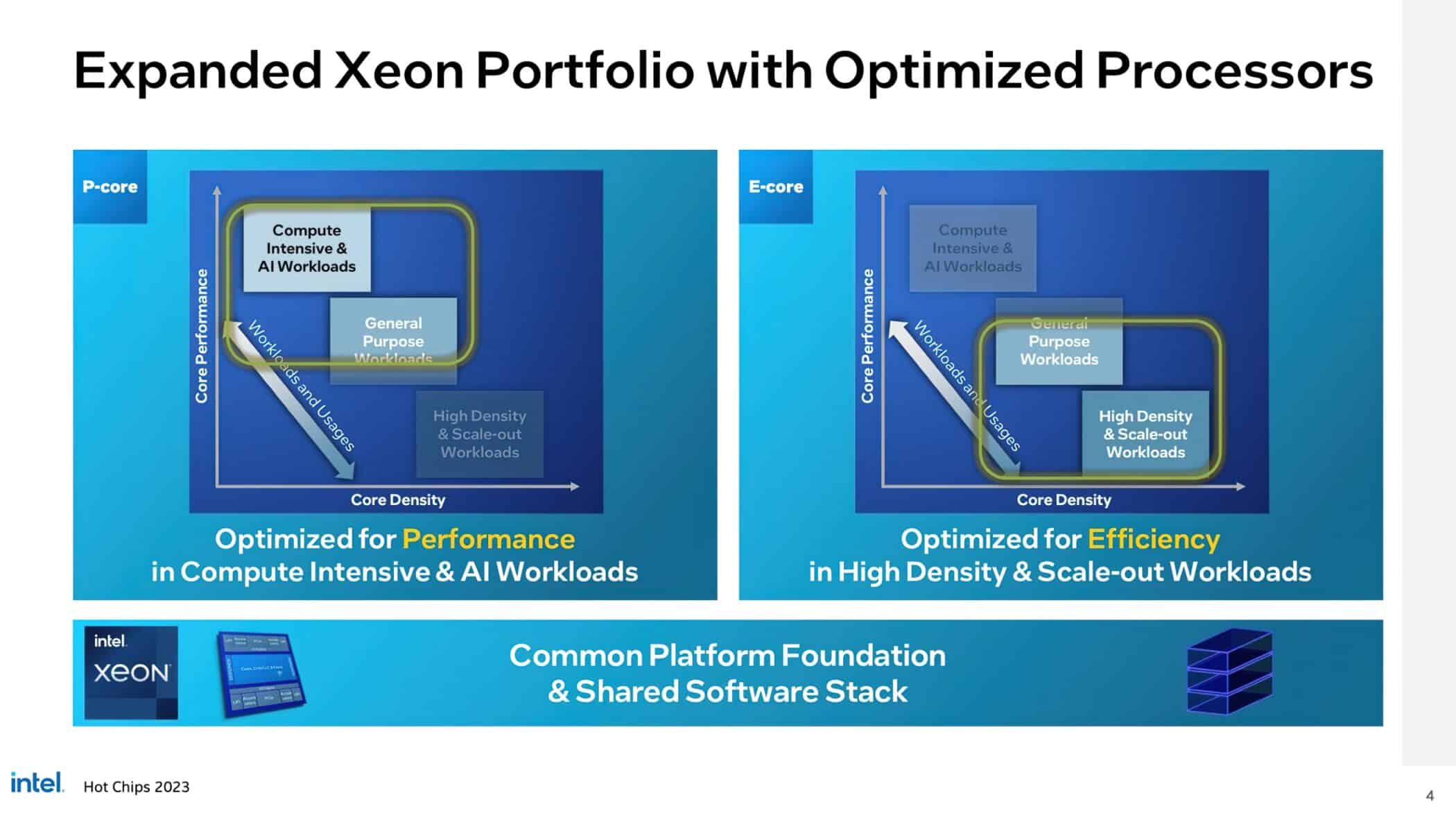

IntelはHot Chips 2023で、今後発売予定の144コアXeon Sierra ForestおよびGranite Rapidsプロセッサの詳細を初めて発表した。前者はIntelの新しいSierra Glen Eコアで構成され、後者は新しいRedwood Cove Pコアを採用している。この次世代Xeonチップは、「Intel 7」プロセス上のデュアルI/Oチップレットと「Intel 3」プロセス上のさまざまな構成のコンピュートコアを組み合わせた新しいタイルベースのアーキテクチャを採用し、来年前半に発売される。この設計により、Intelは同じ基本構成を維持しながら、異なるタイプのコアに基づく複数の製品を製造することができる。

Sierra ForestとGranite Rapidsは、ソケット、メモリ、ファームウェア、I/Oの互換性を備えたBirch Streamプラットフォームに搭載され、ハードウェア検証プロセスを合理化する。また、同じソフトウェア・スタックとの相互運用が可能であるため、顧客はニーズに応じてどちらのチップを採用することもできる利点がある。

Intelは、次世代Xeon Sierra ForestのE-Coreベースの設計は、第4世代Xeonチップに比べてラック密度が最大2.5倍向上し、ワットあたりの性能が2.4倍向上すると主張している。一方、P-Coreを搭載したGranite Rapidsは、AIワークロードの混在処理において2~3倍の性能を発揮し、その一部はメモリ帯域幅の「最大」2.8倍の改善に起因している。

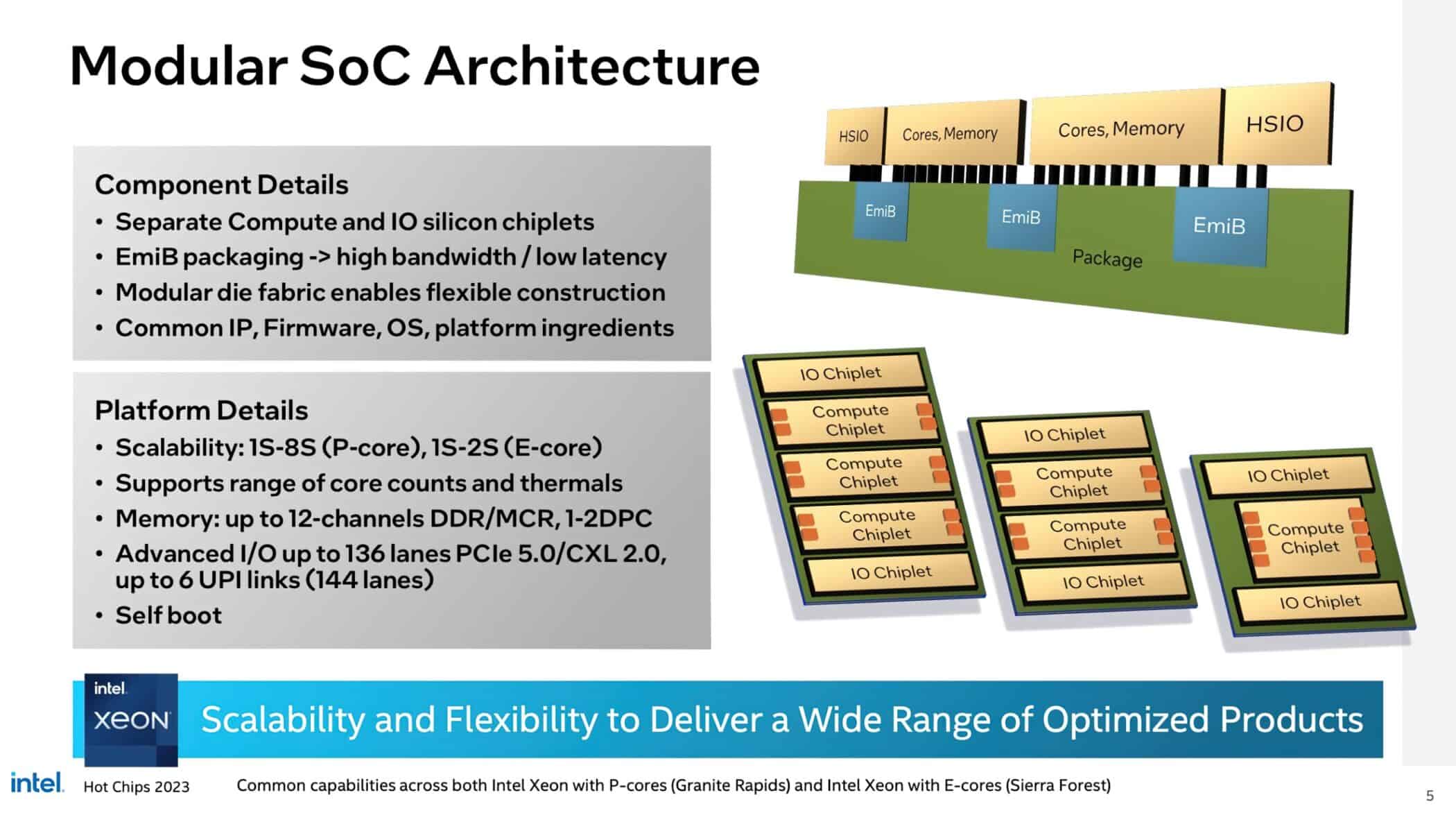

Intelは当初、第4世代Xeon Sapphire Rapidsプロセッサーでタイルベースの(チップレット的な)アーキテクチャに移行したが、Sierra ForestとGranite Rapidsはこのアプローチに新たなレベルの分解をもたらした。

IntelはSapphire Rapidsで4ダイ設計を採用し、各ダイにメモリやPCIeコントローラなどの関連I/O機能の一部を搭載した。新しいプロセッサーは、I/O機能の一部をIntel 7プロセスにエッチングされた2つの独立したHSIOチップレットに完全に分離し、I/Oのコスト、消費電力、性能のベストバランスを提供する。

2つのHSIOダイはチップパッケージの上部と下部に配置され、中央に1~3つのコンピュート・ダイが配置され、基板内で融合された不特定多数のEMIB(Embedded Multi-Die Interconnect Bridge)インターコネクトとブリッジの両端のダイ間インターコネクトに接続されている。

コンピュート・タイルには、Granite RapidsではRedwood Cove Pコア(パフォーマンス・コア)、Sierra ForestではSierra Glen Eコアのいずれかが採用される。このコンピュート・チップレットは、EUVに対応したIntel 3プロセスに搭載され、Intel 4プロセスにはなかった高密度ライブラリを備えている。Intelは当初、設計を「Intel 4」から「Intel 3」に切り替えたため、Granite Rapids Xeonの発売を2023年から2024年に延期したが、チップは2024年前半に発売される予定である。

Granite Rapidsは、我々が伝統的なXeonデータセンター・プロセッサーと認識しているもので、これらのモデルは、Intelの最速アーキテクチャーの性能をフルに発揮できるPコアのみを搭載している。各Pコアには、2MBのL2キャッシュと4MBのL3キャッシュが搭載されている。IntelはGranite Rapidsのコア数をまだ明らかにしていないが、このプラットフォームが1台のサーバーで1ソケットから8ソケットまでサポートすることを明らかにした。

一方、Sierra ForestのEコア(効率性コア)ラインナップは、IntelのAlderやRaptor Lakeチップに見られるように、より小さな効率性コアのみを搭載したチップで構成されており、データセンターで普及しつつあるArmプロセッサに対抗するのに適した位置づけとなっている。Eコアは、4MBのL2キャッシュスライスと3MBのL3キャッシュを共有する2コアまたは4コアのクラスタに配置される。Eコア搭載プロセッサーは最大144コアを搭載し、電力効率、面積効率、性能密度を最大限に高めるよう最適化されている。コア数の多いモデルでは、各Eコアコンピュートチップレットは48コアを搭載しています。Sierra Forestは、シングルおよびデュアルソケットシステムに搭載可能で、TDPは200Wと低い。

コアの種類にかかわらず、各コンピュート・ダイにはコア、L2およびL3キャッシュ、ファブリックおよびキャッシング・ホーム・エージェント(CHA)が搭載されている。また、ダイの両端にはDDR5-6400メモリ・コントローラが搭載されており、標準的なDDRメモリ、または標準的なDIMMよりも30~40%高いメモリ帯域幅を提供する新しいMCRメモリのいずれかを合計最大12チャネル(1DPCまたは2DPC)搭載できる。

上にあるように、コンピュート・チップレットはモデルによってサイズが異なり、シングルコンピュート・ダイ製品にはより大きなコンピュート・クラスタが搭載される。Intelはまた、コンピュート・チップレットあたりのメモリ・チャネル数を変更するようだ。ここでは、コンピュート・チップレットが1つの製品に3つのメモリ・コントローラが搭載されているのに対し、コンピュート・チップレットが2つ以上の設計では、1つにつき2つのメモリ・コントローラが搭載されている。Intelは、コンピュート・チップレットにメモリ・コントローラを緊密に統合するため、AMDのEPYC設計と比較すると、一部のワークロードで優れたメモリ性能を発揮するものと考えられる。AMDのEPYCでは、すべてのメモリ・コントローラを1つの中央I/Oダイに搭載しているため、レイテンシと競合が発生している。

コンピュート・ダイは、Intelが「論理的にモノリシックなメッシュ」と呼ぶ方法で、他のすべてのコアとL3キャッシュを共有するが、特定のワークロードのレイテンシを最適化するために、サブNUMAクラスタに分割することもできる。メッシュはL3キャッシュスライスを統合共有キャッシュに結びつけ、総容量は半分以上のギガバイトとなり、Sapphire Rapidsのほぼ5倍となる。各ダイのバウンダリーは、ダイ間で1TB/秒以上の帯域幅をサポートする。

2つのHSIOダイを組み合わせることで、最大136レーンのPCIe 5.0/CXL 2.0(タイプ1、2、3デバイス)、最大6つのUPIリンク(144レーン)、および圧縮、暗号化、データストリーミングアクセラレータを、Sapphire Rapidsのアクセラレーションエンジンと同様の方法でサポートする。各HSIOダイには、コンピュート・チップレットを管理する電源制御回路も含まれているが、各コンピュート・チップレットは、必要に応じて独立して動作する独自の電源制御も備えている。Intelは今回、チップセット(PCH)の必要性をなくしたため、AMDのEPYCプロセッサーのように、プロセッサーをセルフブートできるようにしている。

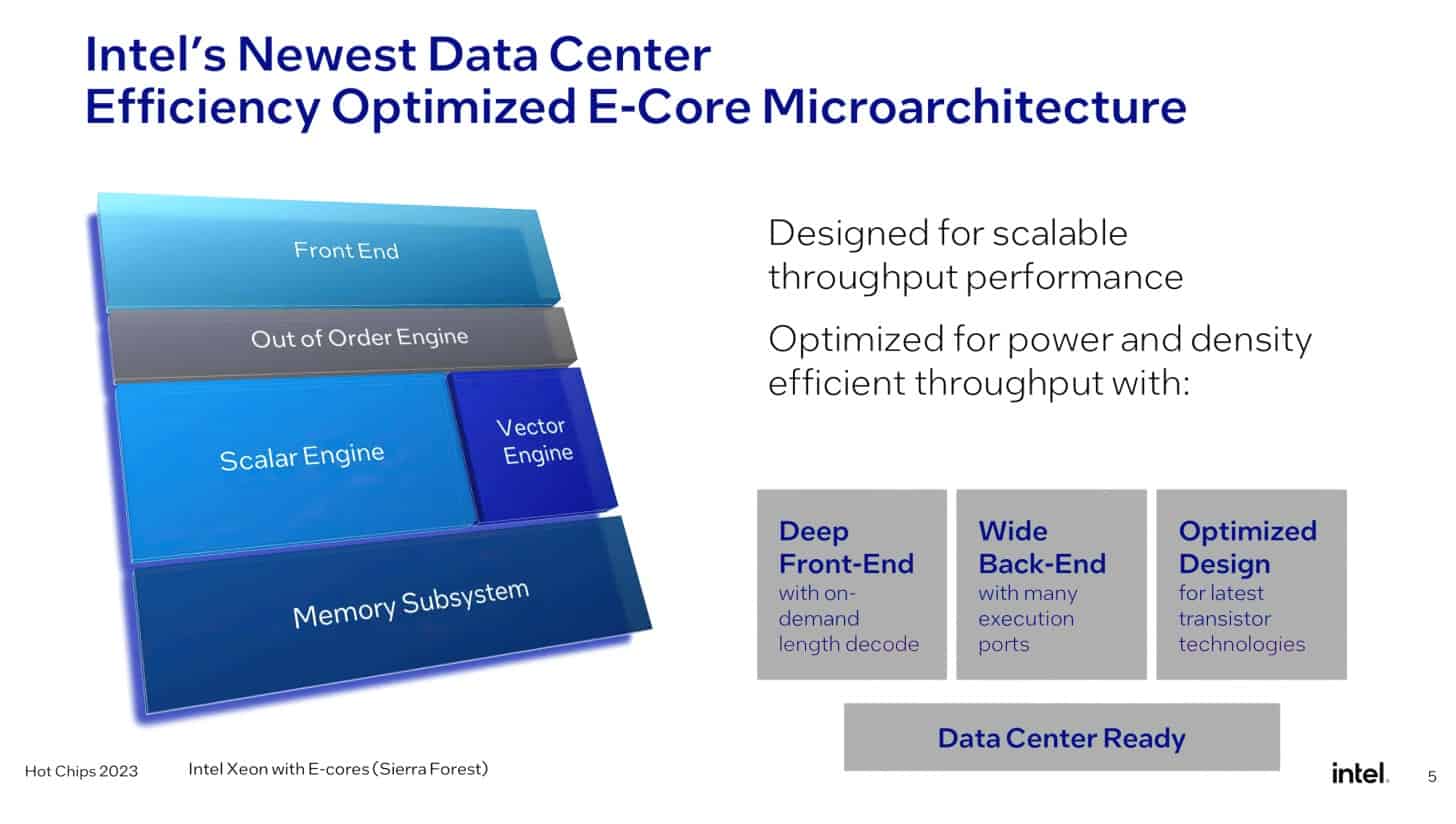

Intel Sierra Glen E-Core マイクロアーキテクチャ

Sierra Glenマイクロアーキテクチャは、スケールアウト、クラウドネイティブ、コンテナ化環境などのスケーラースループットワークロードで最高の効率を発揮するように最適化されている。このアーキテクチャは、2コアまたは4コアのクラスターを備えており、Intelは特定のモデルで、コアあたりのL2キャッシュ容量とコアあたりの性能(2コアモジュールの場合、より高い電力供給)を向上させることが出来る。各コア・クラスターは、同じクロックおよび電圧ドメイン上に存在する。Eコア・クラスタは、4MBのL2キャッシュ・スライスと3MBの共有L3キャッシュを共有する。

旧世代と同様、各Eコアはシングルスレッドである。Intelはまた、L1キャッシュを64KBに倍増し、6ワイドデコードエンジン(レイテンシと消費電力を改善するためデュアル3ワイド)、5ワイドアロケート、8ワイドリタイアを採用している。Sierra GlenコアはAMXやAVX-512をサポートせず、代わりにAVX10に依存するが、IntelはBF16、FP16、AVX-IFMA、AVX-DOT-PROD-INT8のサポートを追加した。

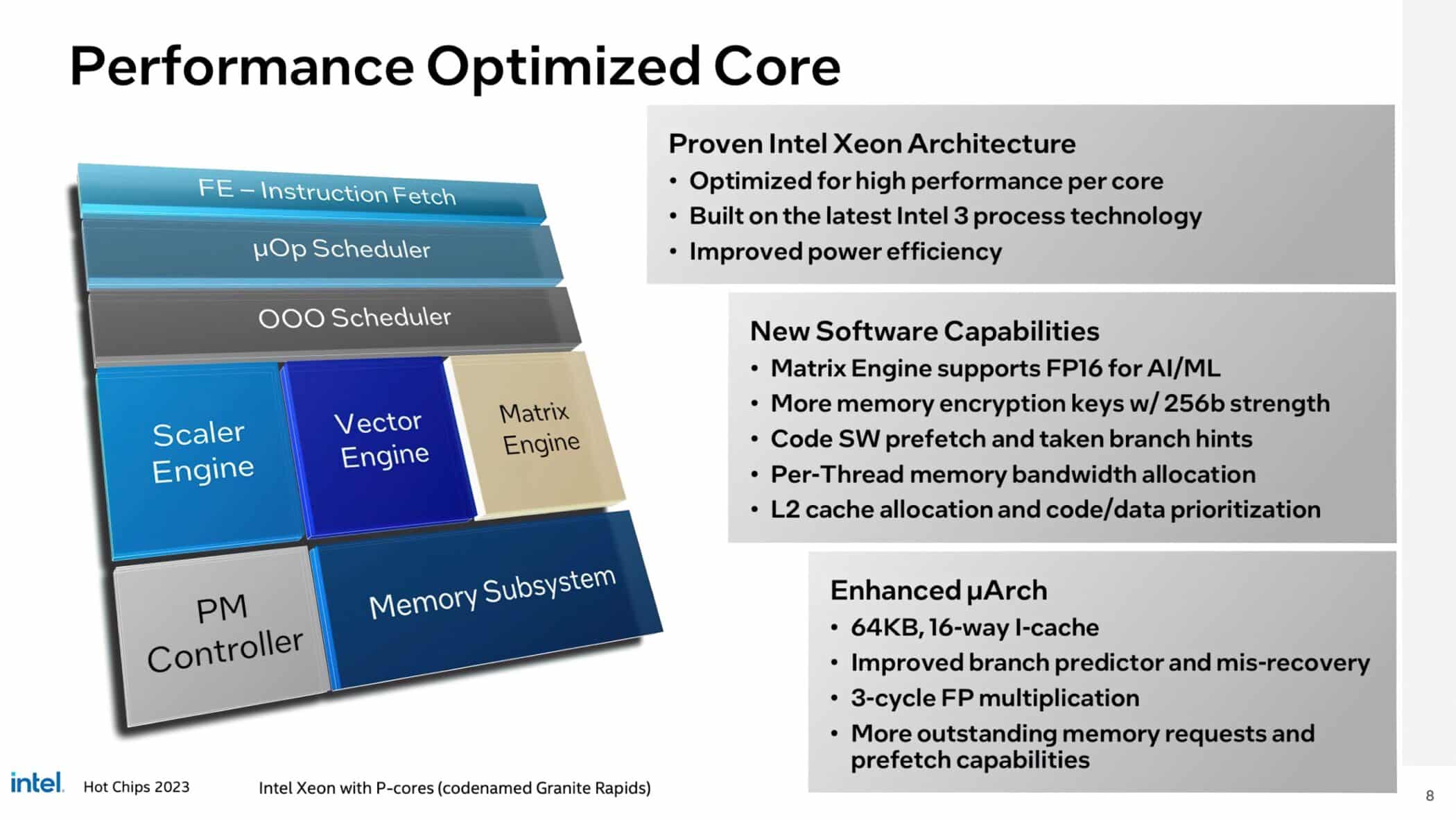

Intel Redwood Cove P-Core マイクロアーキテクチャ

PコアのRedwood Coveアーキテクチャは、FP16アクセラレーションでAMXをサポートするようになった。これは、AI推論ワークロードのパフォーマンスを高める重要な追加機能である。また、IntelはL1命令キャッシュの容量を64KBに倍増し、コード量の多いデータセンターのワークロードへの対応を強化した。Redwood Coveはまた、ソフトウェアで最適化されたプリフェッチと、強化された分岐予測エンジンとミスリカバリーを採用している。Intelはまた、4サイクルおよび5サイクルのFP演算を3サイクルに移行することで浮動小数点演算性能を改善し、IPCを向上させた。

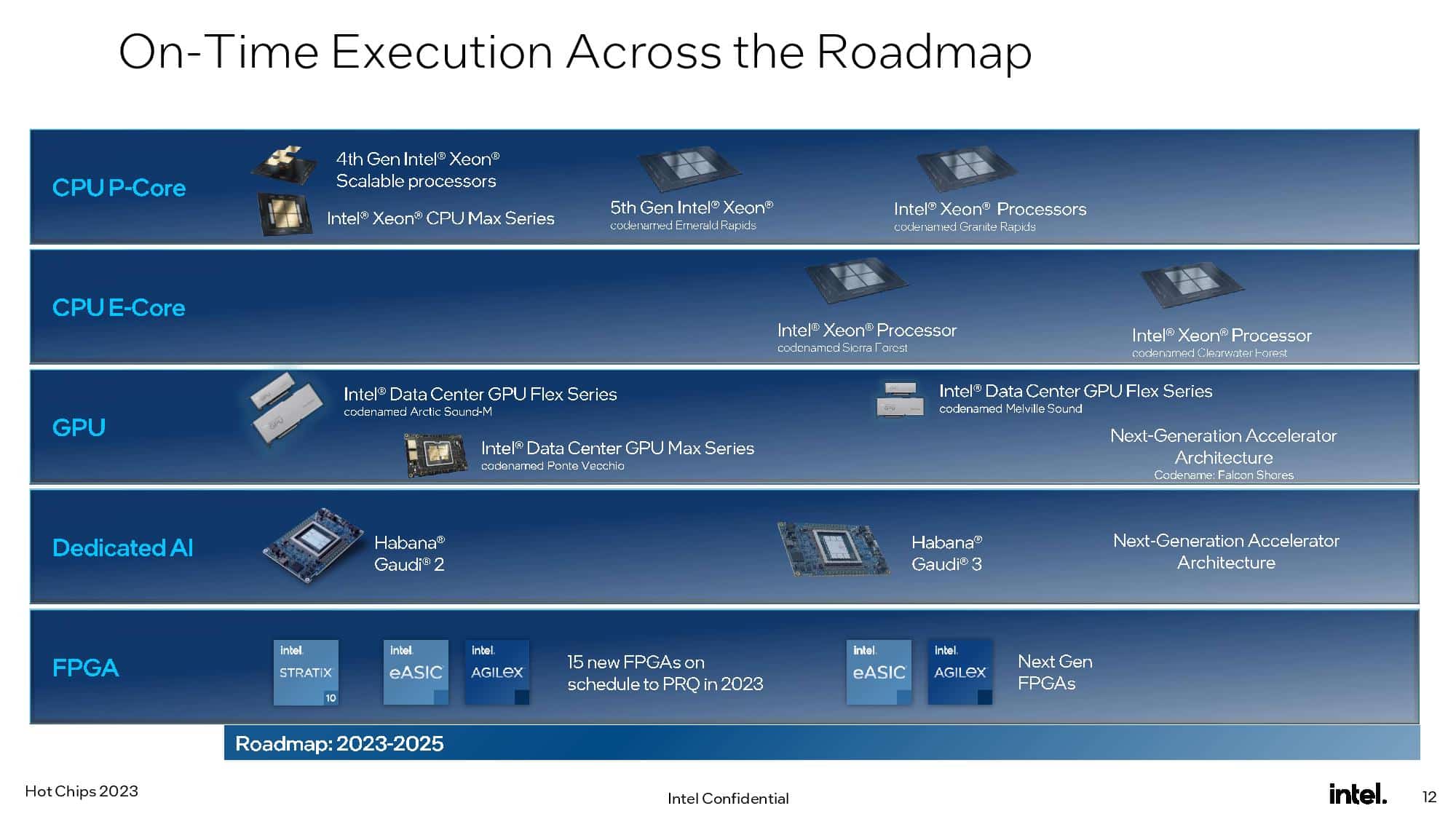

Intel Xeon Roadmap

Intelのデータセンター・ロードマップは順調に進んでいる。Sierra Forestは2024年前半に市場に投入され、Granite Rapidsはその直後に投入される予定だ。

ここでは、IntelのロードマップとAMDのデータセンター・ロードマップを比較している。現在、AMDが昨年発表したEPYC Genoaと、Intelが今年初めに発表したSapphire Rapidsの間で、高性能バトルが繰り広げられている。Intelは、今年の第4四半期にEmerald Rapidsのリフレッシュ世代を発表しており、同社によれば、より多くのコアとより高速なクロックレートを搭載する予定であり、すでにHBMを搭載したXeon Max CPUをリリースしている。AMDは最近、5nmのGenoa-X製品を発表した。来年には、Intelの次世代Granite RapidsがAMDのTurinと対決する。

AMDのBergamoは、AMDの高密度なZen 4cコアを活用することで、Sierra Forestと非常によく似たコアを多用するアプローチをとっている。Bergamoはすでに市場に投入されているが、IntelのSierra Forrestは2024年前半まで登場しない。AMDの第5世代EPYC Turinチップは2024年末までに発売されるが、同社は第2世代Zen 4cモデルの概要を明らかにしていない。Intelは現在、第2世代Eコア搭載のClearwater Forestを2025年のロードマップに載せている。

Sources

コメントを残す