本日、Armは、同社の次世代フラッグシップ・パフォーマンス・コアであり、これまでに設計されたArmコアの中で最も高性能な「Cortex-X4」を発表した。

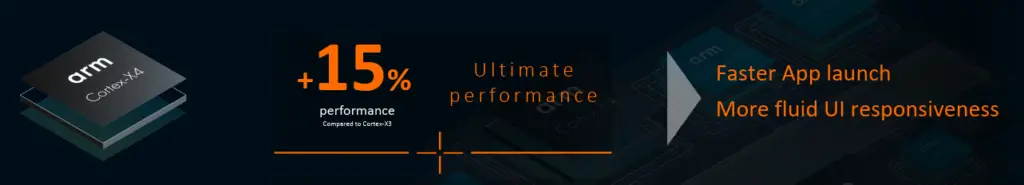

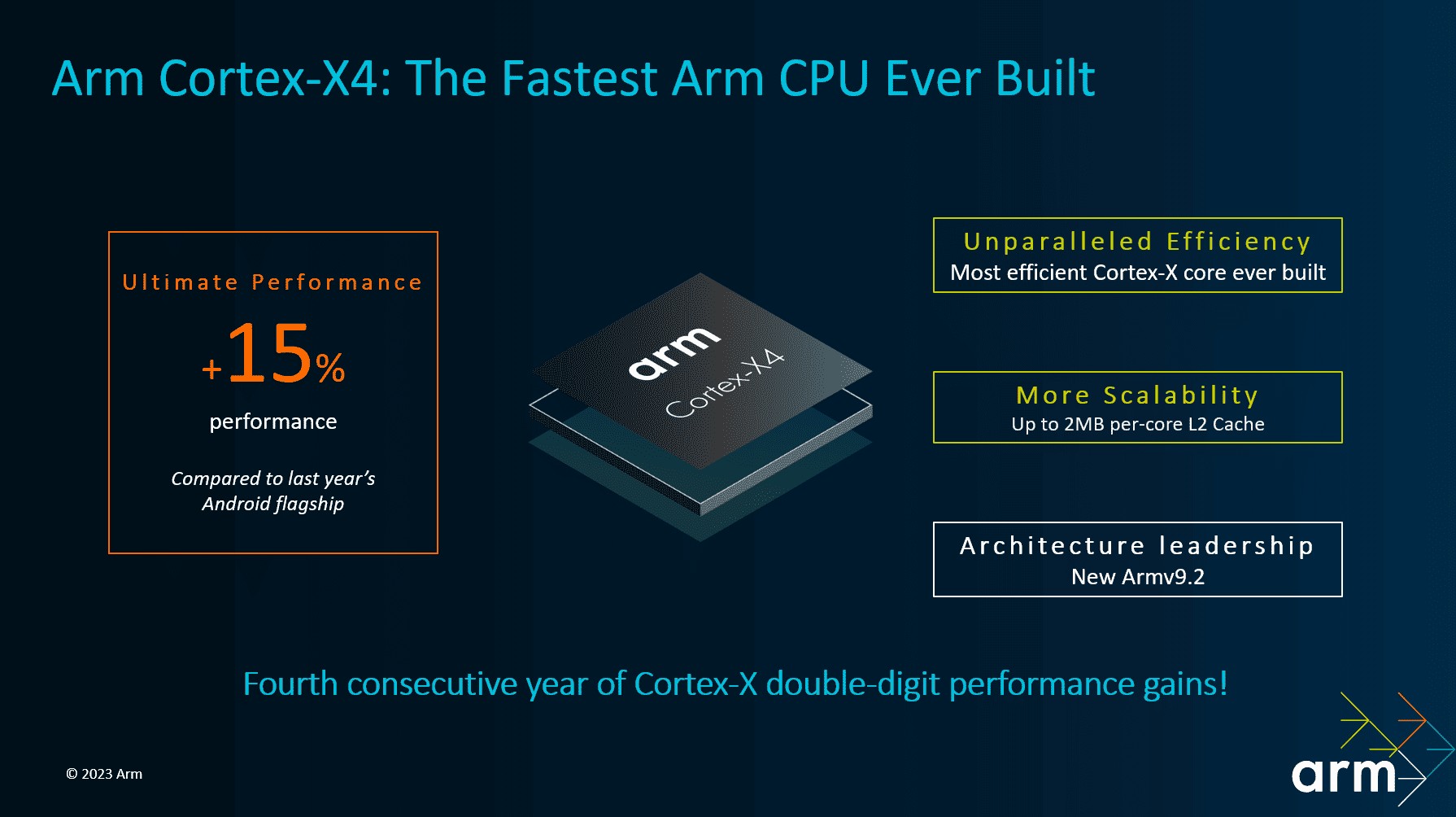

Cortex-X4は、Armの最新フラッグシップコアだ。Armによると、現行世代で、Snapdragon 8 Gen 2等に採用されているCortex-X3と比較して15%の性能向上を実現しているという。Armは、Cortex-Xシリーズの登場以来、“2桁のIPC向上を実現するのは4世代連続である”と述べている。Cortex-X4の性能向上は、同一のキャッシュサイズにおいて10%未満という最小限の面積コストで実現されている。

Cortex-X4は、前モデルと同様に、さまざまなワークロードにおいてCortex-A720が提供する性能以上に必要とされるピーク性能に焦点を当てている。Cortex-X4は、パイプライン全体に及ぶ多くの変更によって性能向上を実現しているとのことだ。

フロントエンド

Armによれば、Cortex-X4のフロントエンドには大きな変更が加えられているとのことだ。具体的には、命令フェッチ配信が完全に再設計されたのだ。

Cortex-A715と同様に、Cortex-X3も、マクロオペレーションキャッシュを完全に廃止したという。その代わり、Cortex-X4ではパイプラインを広げ、最大10命令までサポートするようにした。それに伴い、命令キャッシュも強化された。帯域幅は1サイクルあたり10命令まで向上している。

Armによると、新しい分岐予測器の精度も向上し、実際のワークロードで観察されたストールも測定可能なほど減少している。命令キャッシュとマクロオペレーションキャッシュの変更により、分岐予測ミスのペナルティは統一され、10サイクルに削減された。

バックエンド

アウトオブオーダーのバックエンドも強化されている。実行ユニットの整数側で、Armは前世代のMULユニットをフルMACユニットに更新した。つまり、X4には2つの整数MACユニットがあることになる。また、3つ目のブランチユニットも追加されました。最後に、2つの整数型ALUが追加され、合計8個になった(うち6個は専用パイプ)。

Cortex-X4のアウトオブオーダーバッファは、Cortex-X3の320から、ここでは384に20%増加した。実は、Armは世代ごとにROBを10~30%ずつ増やしている。Cortex-X4のROBは、352エントリーのIntelのSunny Coveコアよりも大きくなっており、512エントリーのROBを持つGolden Coveには及ばないものの、その大きさを物語っている。

| Reorder Buffer(ROB) | ||||

|---|---|---|---|---|

| uArch | Cortex-X1 | Cortex-X2 | Cortex-X3 | Cortex-X4 |

| Dispatch | 8/cycle | 8/cycle | 8/cycle | 10/cycle |

| Max In-flight | 224 | 288 | 320 | 384 |

浮動小数点側では、Armはdivider/sqrtユニットを完全にパイプライン化した。パイプやユニット自体に変更はない。

メモリ

メモリサブシステム側では、Armはパイプのバランスを見直した。Cortex-X3では、2つの汎用AGUと1つの専用ロードAGUがあったが、Cortex-X4では、1つの汎用AGUと、2つのロードAGUと1つのストアAGUがある。

命令キャッシュと同様に、Cortex-X4ではデータプリフェッチャも強化された。Armによれば、新たにL1 temporal data prefetcherも追加されたという。また、Armによれば、L1の変更点として、L1データバンクの競合を減らし、L1 TLBを2倍にしたという。

Cortex-X4のプライベートL2キャッシュも拡大されている。システムインテグレータは、最大2MiBのL2キャッシュを統合することができるようになり、前世代に比べてL2キャッシュが倍増した。システム設計者は、より制限された環境で、より小さなキャッシュサイズを使用することも可能だ。Armは、より大きなキャッシュにはレイテンシヒットがないとしている。このオプションは、頻繁に参照するためにコアの近くにあることを利用できる、大きなメモリフットプリントを持つアプリケーションでより高いパフォーマンスを可能にする。

全体として、Cortex-X4はISO-frequencyとL3(L2が大きいとはいえ)で約13%のIPC向上を実現している。

Armは、Cortex-X4は、たとえばTSMCのN3E 3nm製造プロセスを使用して製造できると述べており、このCPUコアがどの程度ハイエンドに設定されているかが窺える。

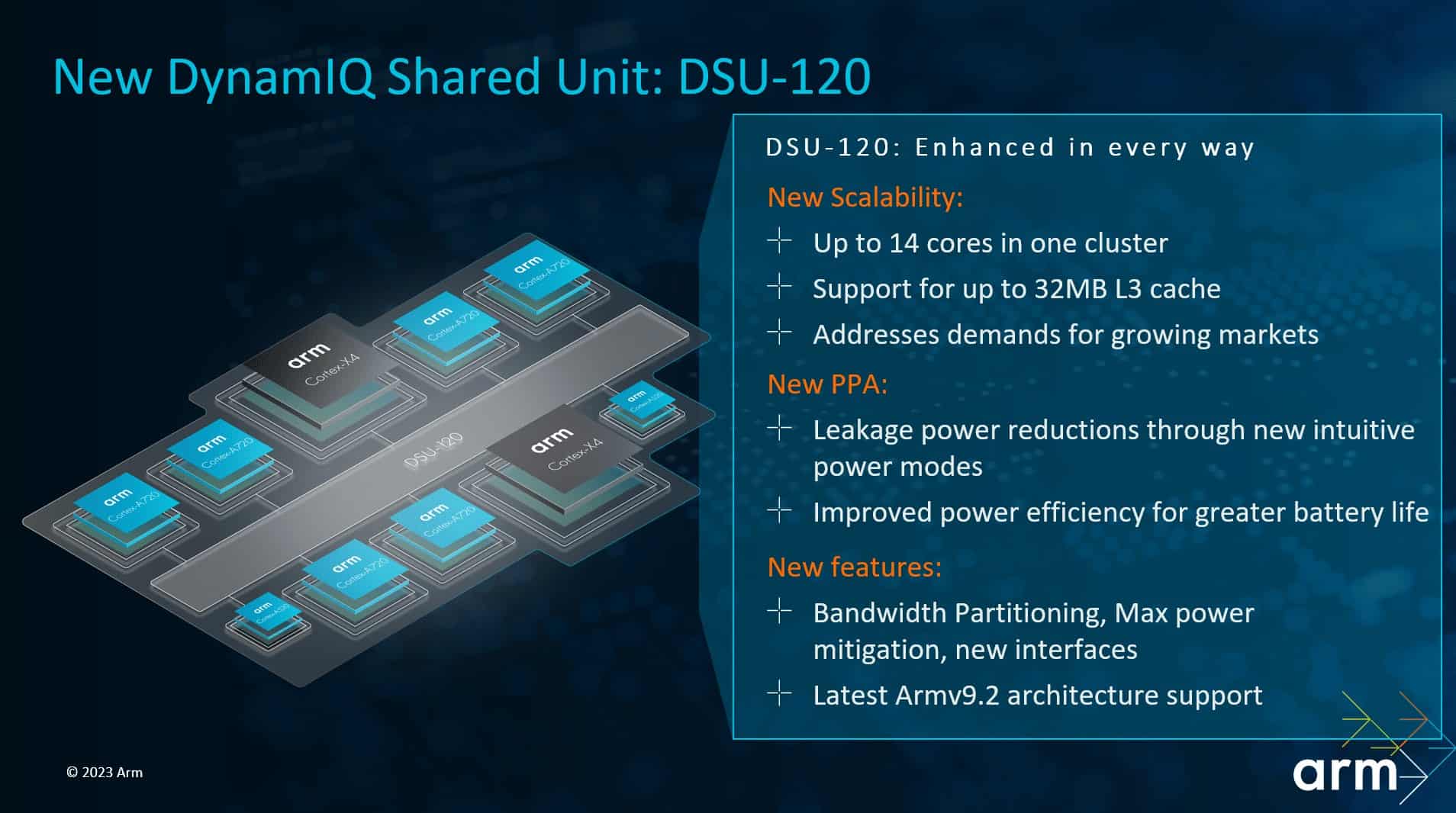

コアクラスタを束ねるDSU-120は、最大32MBの共有L3キャッシュに対応したほか、リーク電力の低減に役立つ新しい電力モードを搭載した。これには、CPUコアがアイドル状態のときにメモリを低電力状態にする機能が含まれている。

また、DSU-120は、Cortex-X4、Cortex-A720、Cortex-A520を自由に組み合わせたより柔軟なコア構成を可能にし、ノートパソコンによく搭載されるCortex-X4 10個とCortex-A720 4個の構成も可能だ。

Source

コメントを残す