6月11日から16日にかけて開催される予定のVLSIシンポジウム2023において、Intelは、Intel 4ノードを用いて製造されたE-Coreチップ上で、同社が初採用する裏面電力供給テクノロジー「PowerVia」が効率的に動作する様を実証したサンプルを展示するようだ。

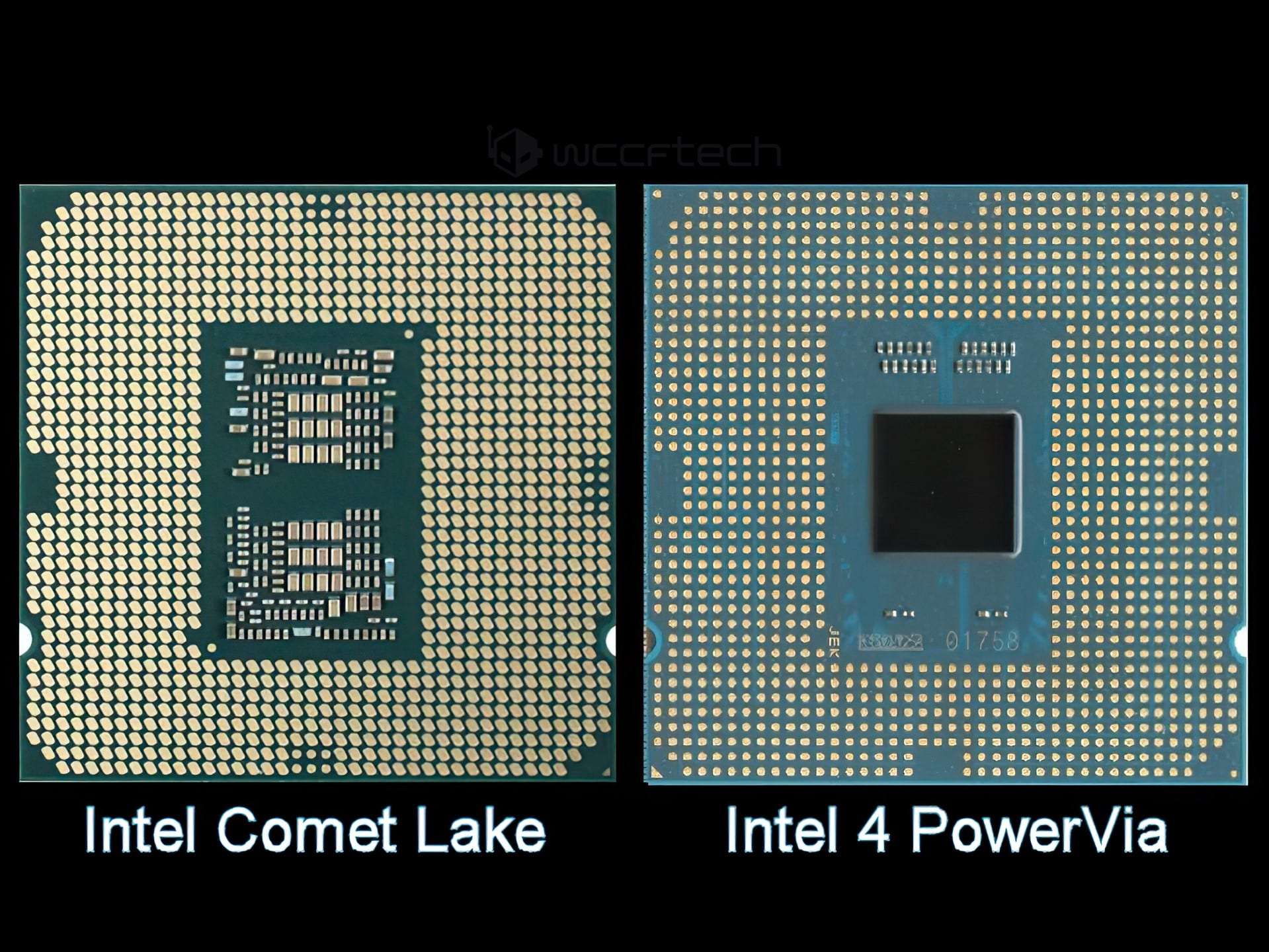

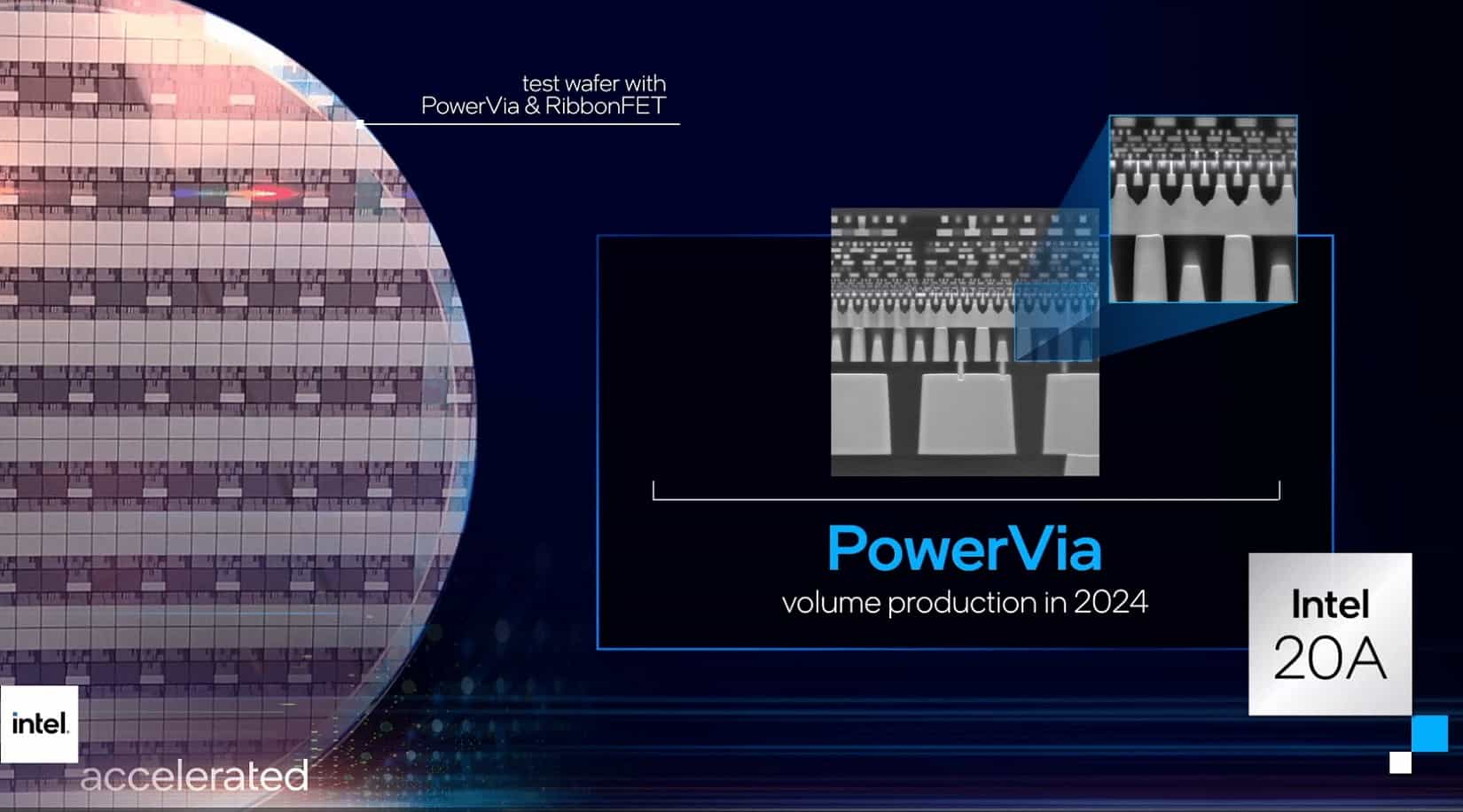

従来のチップは、電源と信号の相互接続が複数の金属層に分散している。一方、PowerViaは、電力供給用に特定の層を専用化し、信号配線層から効果的に切り離す。このアプローチでは、電力専用のTSV(Through-Silicon Vias)またはPowerVia(チップの上面と下面の間の垂直接続)を通して、垂直電力伝送が可能になる。チップの裏面から直接電力を供給することで、PowerViaは電源ノイズと抵抗損失を減らし、電力分配を最適化し、全体的なエネルギー効率を改善する。PowerViaは、2024年にIntel 20Aノードでデビューする予定だ。

VLSI Symposium 2023の講演では、Intel 4テクノロジーで作られ、テストチップにのみE-Coreを実装した設計を紹介する論文を用意したそうだ。その資料にはこう書かれている:「PowerViaテクノロジーは、Power Deliveryを裏側に持つことで、Process Scalingを拡張する新しいイノベーションです。本論文では、PowerViaテクノロジーでIntelE-Coreを実装して、シリコン前とシリコン後の調査結果を示す。PowerViaは、コアの広い領域で90%以上のスタンダードセル利用を可能にし、IRドロップの減少によりシリコンで5%以上の周波数利益を示しました。ポストシリコンデバッグの成功は、スループット時間が若干長くなるものの、許容範囲内であることを実証しています。PowerViaテストチップの熱特性は、ロジックの微細化によって予想される高い電力密度に見合ったものでした」。

PowerViaは、周波数の向上やIRドロップの低減だけでなく、熱管理も大きなメリットとなる。ロジックのスケーリングが進むと、より多くのトランジスタがより小さなスペースに詰め込まれるため、熱密度が高くなる。PowerViaはその問題を小さくし、より効率的に熱を逃がすことを可能にするはずです。PowerViaはIntel 20Aノードで予定されているにもかかわらず、Intel 4ノードで実装したのは、Intel Foundry Service(IFS)の顧客に対して、その仕組みや実装方法を学び、提示するためのようだ。

Source

- Tom’s Hardware: Intel to Show Off E-Core-Based CPU with Backside Power Delivery

コメントを残す