第68回IEEE International Electron Devices Meeting (IEDM)がサンフランシスコにて開かれ、世界中の半導体研究者・エンジニアが一堂に会し、多くの情報交換や議論を交わした。その中でTSMCが提出した論文はあまり注目されていないようだが、今後の半導体、特にCPUとGPUの価格に大きな影響を与えそうな内容のようだ。

- WikiChip Fuse: IEDM 2022: Did We Just Witness The Death Of SRAM?

- Tom’s Hardware: TSMC’s 3nm Node: No SRAM Scaling Implies More Expensive CPUs and GPUs

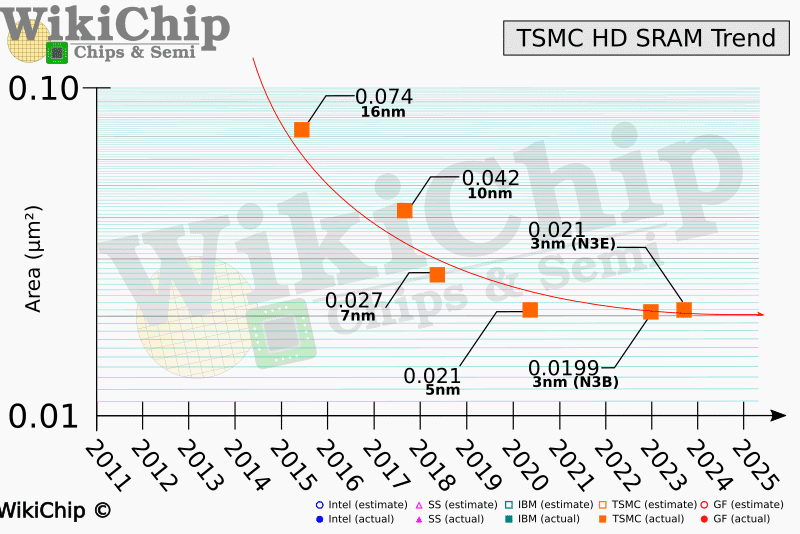

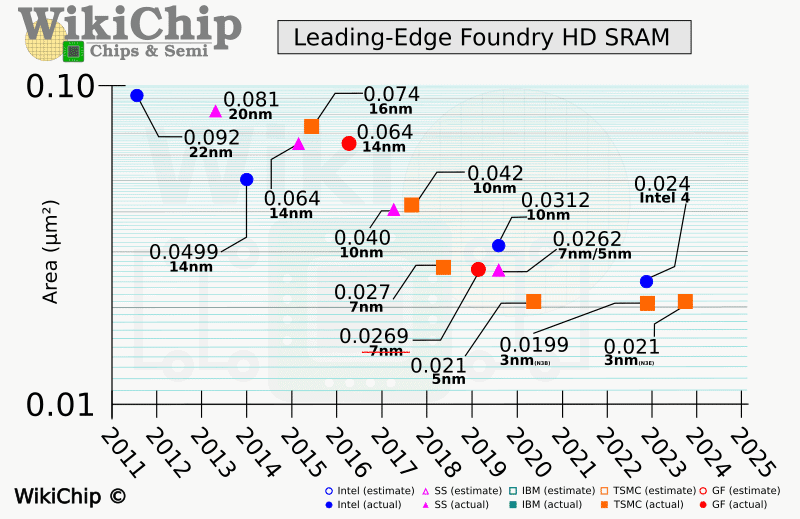

新しい製造ノードが導入されると、性能の向上、消費電力の削減、トランジスタ密度の向上が期待される。だが、WikiChipのレポートによると、ロジック回路は最近のプロセス技術で順調にスケーリングされているが、SRAMセルのスケーリングは遅れており、TSMCの3nmクラスの製造ノードではほとんどスケーリングが止まっているとのことだ。

WikiChipによると、カンファレンスにおいて、TSMCは、3nmプロセス世代となる、オリジナルのベースN3(N3B)ノードと、N3Bの拡張版(N3E)の両方について説明している。この中で、注目すべきはN3Eで、SRAMのビットセルサイズが全くスケーリングされていないのだ。具体的には、0.021μm²で、N5ノードと全く同じビットセルサイズのままだという。N3BでのSRAMビットセルサイズではわずかに縮小が見られたが、それでも0.0199μm²と、わずか5%の縮小(または0.95倍の縮小)とのことだ。

大まかなメモリ密度(ISOアシスト回路のオーバーヘッドを想定)は、N3Eが31.8Mib/mm²で、33.55Mib/mm²と1.75Mib/mm²(230キロバイト)の向上が見込まれるとのこと。

N3B と N3E は、チップレベルのトランジスタのスケーリングを 1.6 倍と 1.7 倍にするとされていたが、SRAM のスケーリングが 1.0 倍と 1.05 倍であれば、これは将来のCPU、GPU、SoCにとって大きな問題になる可能性がある。

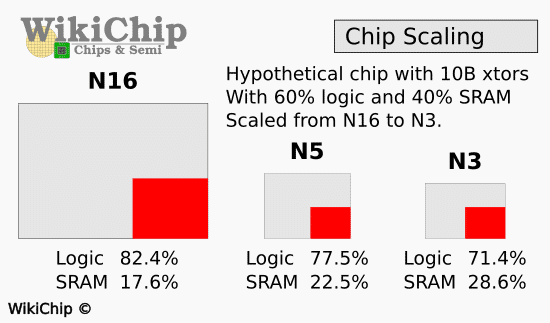

例えば、TSMCの N16で製造された、100億トランジスタのチップがあり、40%をSRAMが、60%をロジック回路が占める製品を考えてみよう。ダイ面積は約255 mm²で、そのうち45 mm²、17.6%がSRAMで占められている事になる。全く同じチップをN5に縮小すると、ダイ面積は56 mm²のチップになり、12.58 mm²(22.5%)をSRAMに充てることができる。さらにこれをN3にまで縮小した場合、ダイ面積は44 mm²となるが、SRAMのスケーリングが行われないため、SRAMが占める面積はN5と同じ12.58 mm²となり、逆にSRAMが面積のほぼ30%を占めるようになってしまうのだ。

今後、キャッシュやSRAMの必要性は高まる一方だが、N3(一部の製品のみに採用される予定)やN3Eでは、SRAMが占めるダイ面積を減らすことはできず、N5に比べて新ノードのコストアップを緩和することもできない。つまり、高性能プロセッサのダイサイズが大きくなり、その分コストも上がるということだ。

SRAMの割合は、ターゲットとなる市場などによって異なるが、現代のCPU、GPU、SoCは、大量のデータを処理するため、特にさまざまな人工知能(AI)や機械学習(ML)のワークロードでは、メモリからデータをフェッチするのは極めて非効率的であるため、各種キャッシュ用に大量のSRAMを使用している。そういった分野では、この影響が他の企業よりも早く出る可能性がある。

また、汎用プロセッサやグラフィックスチップ、スマートフォン向けのアプリケーションプロセッサでも、巨大なキャッシュを搭載しているケースが増えている。例えば、AMDのRyzen 9 7950Xは合計81MBのキャッシュを搭載している。また、NVIDIAのAD102はNVIDIAが公開している各種キャッシュに少なくとも123MBのSRAMを使用している。

この問題はTSMCのみならず、IntelのIntel 4(当初は7nm EUVと呼ばれていた)では、SRAMビットセルのサイズがIntel 7(以前は10nm Enhanced SuperFinと呼ばれていた)の場合の0.0312μm²から0.024μm²に縮小しているが、以前のスケーリングに比べて減速している。

TSMCは、SRAMのビットセルサイズをN5よりも縮小した、N3Sプロセス技術の導入を計画しているが、これは2024年頃に実現することになっている。

コスト面でSRAMのエリアスケーリングの遅れを緩和する方法の1つは、マルチチップレット設計を行い、より大きなキャッシュをより安価なノードで製造された別のダイに分割することだ。これは、AMDが3D V-Cacheで行なっていることだ。もう1つの方法は、キャッシュにMRAM、FeRAM、NRAM、RRAM、STT-RAM、PCMなどの新たなメモリ技術を活用することだ。これらの新しいメモリ・ビットセルは、SRAM と比較して、低い読み書き仕様での高密度化、不揮発性機能、低い読み書きサイクル機能、または潜在的に低い密度や速度での低電力など、独自のトレードオフを提供する。SRAM の直接的な代替品にはならないが、将来的には、低性能のトレードオフを高密度化によって相殺できるレベル 4 またはレベル 5 キャッシュとしての役割を果たす可能性があるだろう。

コメントを残す