Chosun Daily(朝鮮日報)は、Samsung Foundryが、SF3として知られる第2世代3nm GAAプロセス技術によるチップの試作を開始した可能性があると、匿名の業界関係者の話を引用して報じている。現在はチップの性能と信頼性をテストしているが、今後は第2世代の3nmプロセスの歩留まりで60%以上を達成する事を目指しているとのことだ。

Samsungの第2世代3nmプロセス「SF3」を採用する最初の製品は、ウェアラブル向けのアプリケーション・プロセッサーと言われており、今年後半に発売予定の次期Galaxy Watch 7に採用される可能性があるとの事だ。また、来年発売予定のGalaxy S25シリーズ・スマートフォン向けExynos 2500チップにもSF3ノードを使用する見込みだ。

Samsungは、SF3により、同じセル・タイプ内で異なるゲート・オール・アラウンド(GAA)トランジスタ・ナノシート・チャネル幅が可能になり、設計の柔軟性が高まると考えている。これにより、設計を最適化することで、低消費電力と高性能を必要とする回路の実現やトランジスタ密度の向上が可能になる。ちなみに、Samsungの第1世代3nmプロセス「SF3E」は、中国の暗号資産マイニングチップにのみに使用されていると言われている。

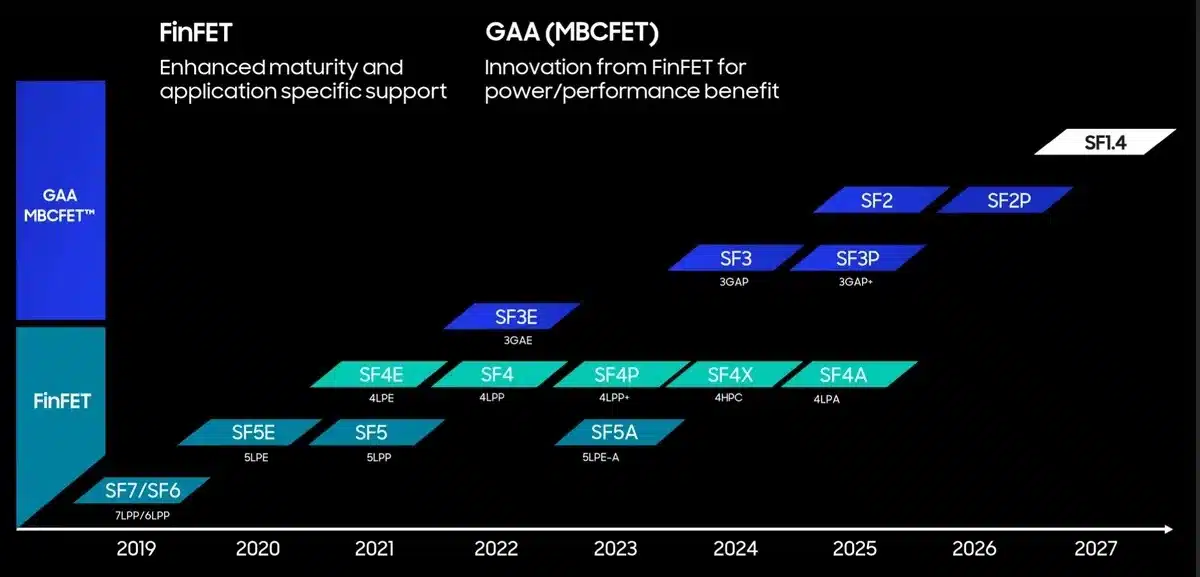

2023年11月に発表されたSamsungのロードマップでは、2024年後半にSF3(第2世代3nmクラス)の生産ノードでチップの量産(HVM)を開始するというものだった。もし今回の報道が事実であれば、Samsungは計画通りに開発を進めているという事になる。

ただし、Tom’s Hardwareは、朝鮮日報がトランジスタ数、ダイサイズ、性能(クロックなど)、消費電力(リーク電流など)、さらにはセルライブラリ(高性能、高密度など)、SRAMとロジックの比率など、他の目標値を開示することなく、仮想テストチップの歩留まり目標を60%としている点を指摘している。

レチクル・サイズ(858mm2)のチップの歩留まりが60%であれば、妥当だが、小型チップの歩留まりが60%であればプロセス技術の欠陥密度が高すぎることを意味し、最新のプロセス技術の場合、商業的には受け入れられない。ファウンドリとチップ設計者は、歩留まりを向上させるために両方を調整する必要があるだろう。

SF3の歩留まり目標に関しては不確定要素が多い為、更なる詳細が待たれる所だが、一方、SF3を使ってSFがリスク生産を開始したという事実は興味深いところだ。

市場調査会社TrendForceによると、昨年第3四半期、TSMCは世界のファウンドリー市場で57.9%のシェアを占めていた。Samsung Foundryはシェア12.4%で2位を確保し、両社の間にはまだ大きな隔たりが存在する。

Sources

コメントを残す