Intelは本日、第4世代のXeon Scalable CPU 「Sapphire Rapids」(通常版とHBM搭載Max版)および「Ponte Vecchio」データセンターGPU Max Seriesを正式に発表した。この52の新しいCPUからなる幅広いポートフォリオは、昨年デビューしたAMDのEPYC Genoaのラインアップと対決することになる。また、Optane Persistent Memory DIMMの最終ラインアップも静かに発表している。

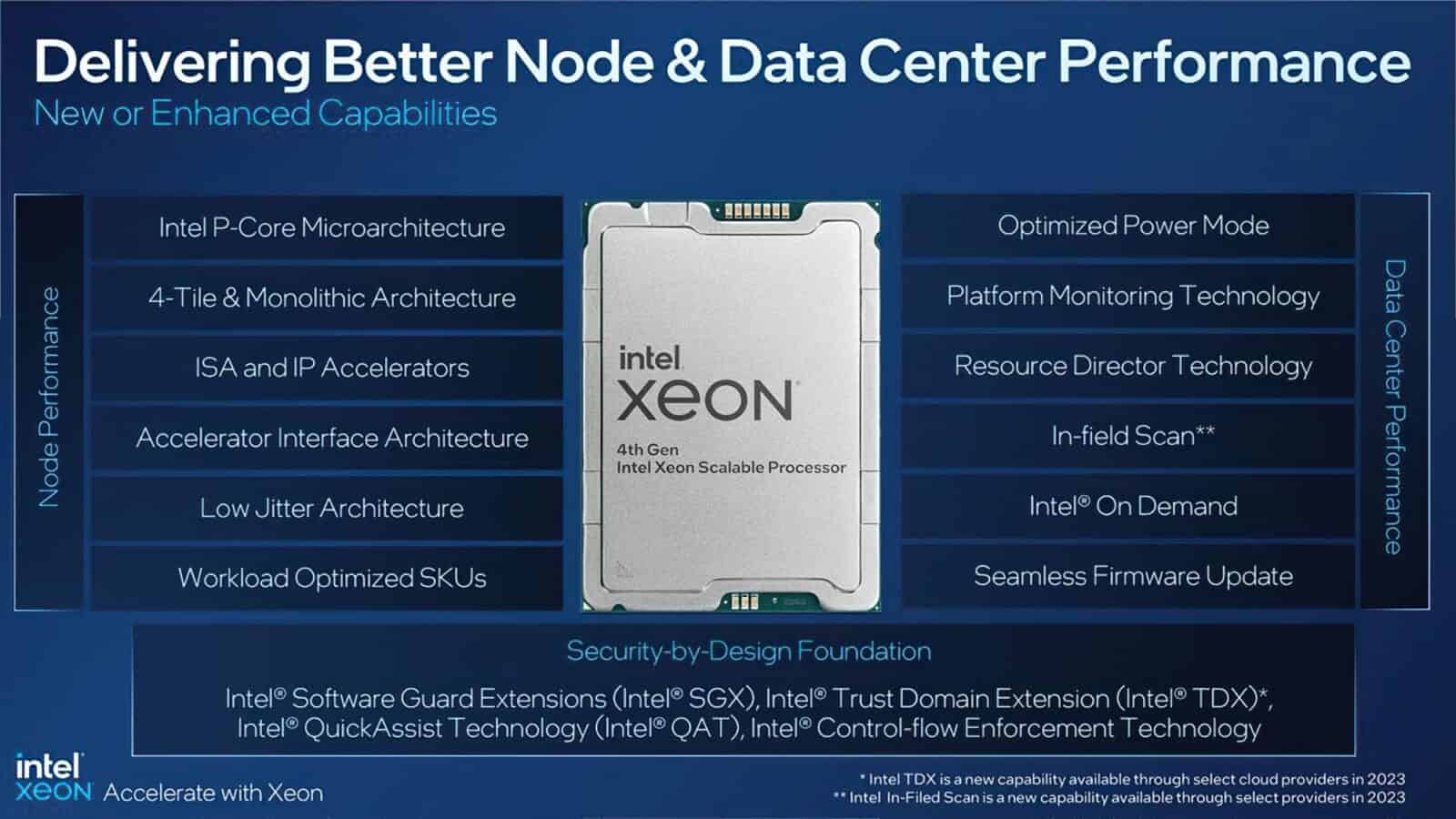

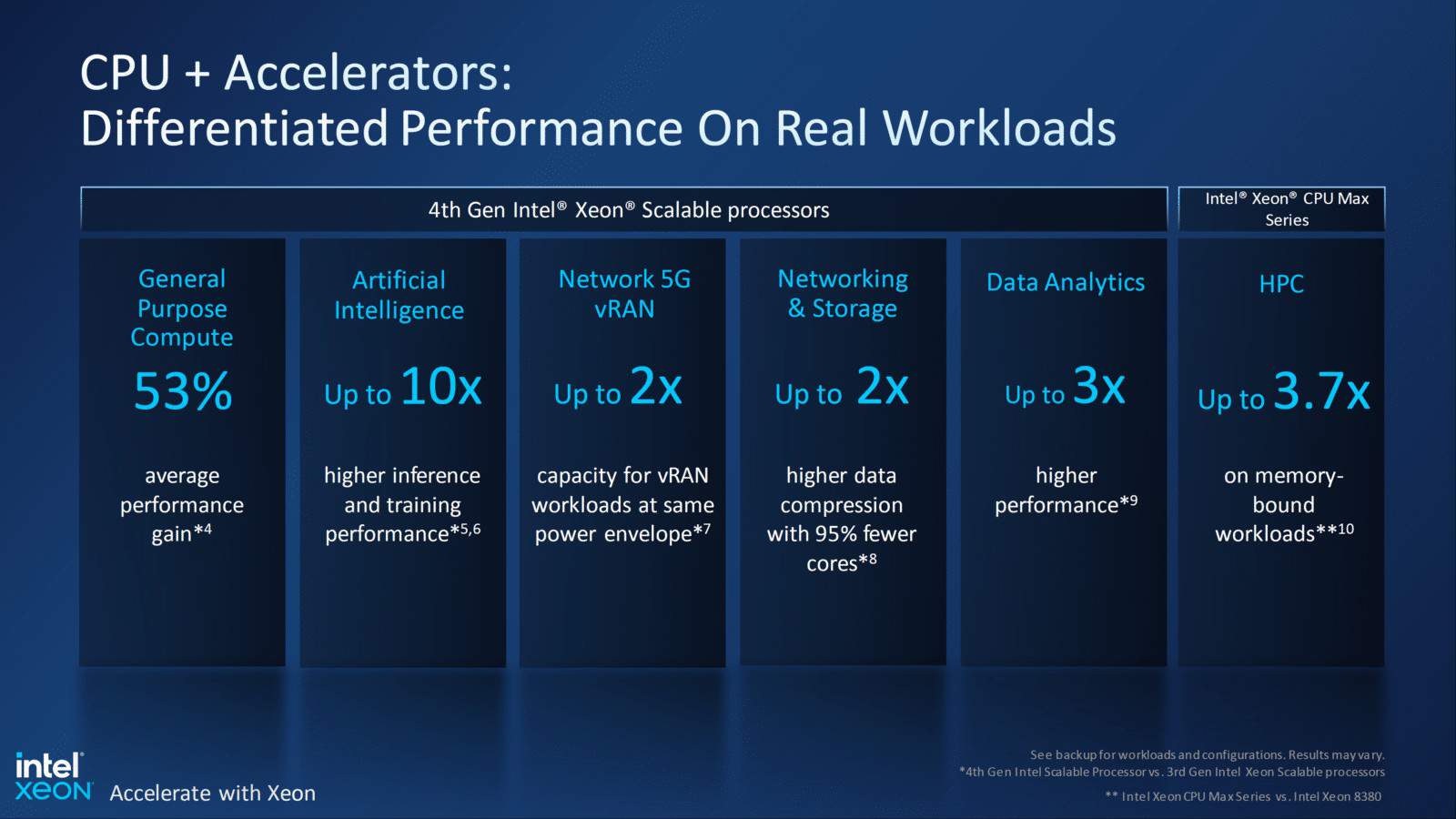

AMDのチップは1チップで最大96コアとコア数においてはリードしているが、IntelのSapphire Rapidsチップでは最大60コアとなり、第3世代Ice Lake Xeonのピーク時の40コアから50%増加している。Intelはこれにより、一般的な演算性能が前世代のチップに比べて53%向上するとしているが、発表会ではAMDのチップとの直接的な比較は行われなかった。

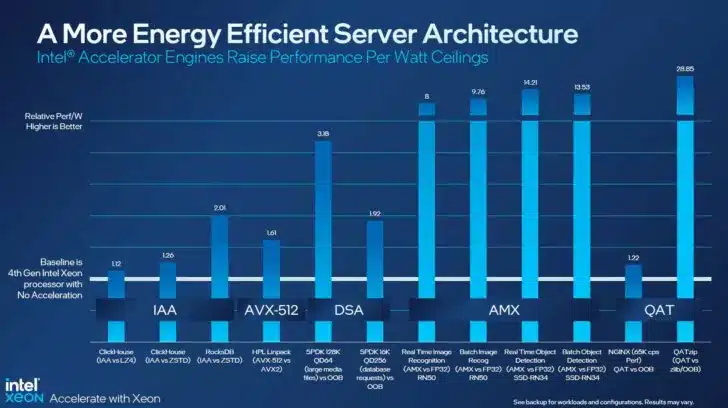

Sapphire Rapidsは、新しいアクセラレーション技術に大きく舵を切っており、これは、そのまま購入するか、新しい従量課金モデルを通じて購入することができる。これらの新しい専用アクセラレーター領域は、圧縮、暗号化、データ移動、データ分析など、最大限のパフォーマンスを得るために通常ディスクリートアクセラレーターを必要とする作業において、性能を根本的に向上させるように設計されている。

AMDはコア数で明らかにリードしているにもかかわらず、Genoaプロセッサーに同様のアクセラレーション機能を搭載していない。新しいアクセラレータを採用した場合、Intelは、一部のワークロードにおいて、自社の旧世代モデルよりもワット当たり性能が平均2.9倍向上するとしている。また、AI推論とトレーニングでは10倍、データ分析ワークロードでは3倍の改善が見込めるとしている。

Intel 7プロセスで製造されるIntelのSapphire Rapidsは、PCIe 5.0、DDR5メモリ、CXL 1.1インターフェース(タイプ1および2デバイス)のサポートといった新しい接続技術にも対応している。新ラインナップの概要は以下の通りだ。

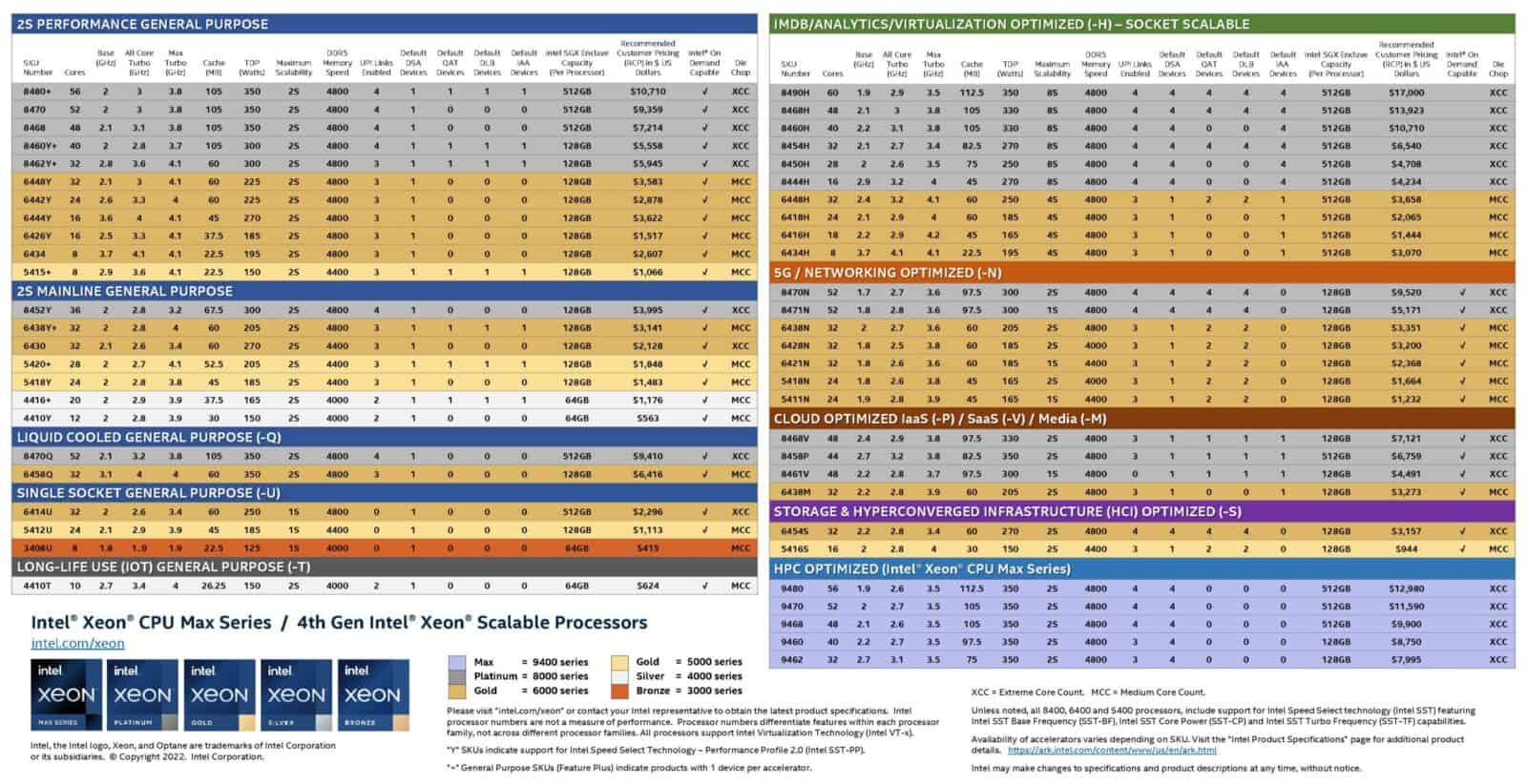

Intel 第4世代XeonスケーラブルSapphire Rapidsの価格と仕様

IntelのSapphire Rapids製品群は、「パフォーマンス」と「メインストリーム」のデュアルソケットチップに切り分けられた52モデルで、汎用モデル向け。また、水冷、シングルソケット、ネットワーク、クラウド、HPC、ストレージ/HCIなどのシステム向けに特化したモデルもある。その結果、ほぼすべてのワークロードに特化したチップが存在するが、ラインナップは複雑ともなっている。

これらのチップは、Max、Platinum、Gold、Silver、Bronzeの各レベルに分類され、それぞれ、ソケット拡張性、Optane永続メモリのサポート、RAS機能、SGXエンクロージャの容量など、さまざまなレベルを示している。

また、Sapphire Rapidsチップには、さまざまな数の有効なアクセラレータデバイスが搭載されるようになった。各チップは有効なアクセラレータ「デバイス」の数を変更でき、それによって性能が異なる。

すべてのアクセラレータに4つのデバイスを搭載した完全な形のチップを購入することも、有効なデバイスの数が少ない安価なチップモデルを選択することも可能だ。チップが完全に有効化されていない場合、Intelオンデマンドと呼ばれる新しい従量課金の仕組みによって、後でアクセラレータを有効にすることができる。各モデルでは、デフォルトで各タイプのアクセラレータが少なくとも1つ有効になっている。しかし、チップには2つのクラスがあり、アクセラレータの割り当てが2種類ある。

新しいプロセッサは、いずれもAVX-512、Deep Leaning Boost(DLBoost)、新しいAdvanced Matrix Extensions(AMX)命令をサポートしており、後者はタイルと呼ばれる新しい2次元レジスタのセットを使用することにより、AIワークロードの性能を爆発的に向上させることができる。IntelのAMX実装は、主にAIのトレーニングと推論操作のパフォーマンスを高めるために使用される予定だ。

従来通り、Intelの第4世代Xeon Scalableプラットフォームは1ソケット、2ソケット、4ソケット、8ソケットの構成をサポートしているが、ライバルのAMDのGenoaは2ソケットまでしか拡張できないようになっている。PCIe接続オプションではAMDがリードしており、最大128レーンのPCIe 5.0接続が提供され、Sapphire Rapidsは最大80レーンのPCIe 5.0接続までとなる。

また、Sapphire Rapidsは1ソケットあたり8チャネルで最大1.5TBのDDR5-4800メモリをサポートし、AMDのGenoaは12チャネルで最大6TBのDDR5-4800メモリをサポートしている。Intelは2DPC(DIMMs per Channel)の構成をDDR5-4400で仕様化しているが、AMDは2DPCの転送速度の認定が終わっていない(同社は今四半期に2DPCの仕様を公開する予定)。

Sapphire Rapidsプロセッサは、8コアモデルから60コアまであり、価格は415ドルから、フラッグシップのXeon Scalable Platinum 8490Hの17,000ドルまでとなっている。8490Hは、60コア120スレッドで、4種類のアクセラレータがすべてフルに有効だ。また、112.5MBのL3キャッシュを搭載し、TDPは350Wとなっている。

Intel Xeon Sapphire Rapids

Sapphire RapidsのTDPエンベロープは、120Wから350Wまでとなっている。350Wという定格は、Intelの前世代Ice Lake Xeonシリーズでのピーク280Wを大幅に上回るものだが、性能向上のための不可避なプッシュにより、業界全体がより高い限界に挑戦しているのだ。例えば、AMDのGenoaは、96コアモデルとはいえ、同様の360WのTDPが最高値であり、400Wまで構成することも可能である。

60コアのモデルは8490Hのみで、すべてのアクセラレーションエンジンを有効にした状態でのみ利用可能だ。56コアのPlatinum 8480+にステップバックすると10,710ドルになるが、この場合は各種アクセラレーションデバイスが1つずつしか有効にならない。このプロセッサは、ブーストクロックが3.8GHz、TDPが350W、L3キャッシュが105MBだ。

IntelのSapphire Rapidsプロセッサでは、新たにオンダイ・アクセラレータが重要な新要素として採用されている。前述したように、アクセラレータのオプションをすべて有効にした状態でチップを購入するか、安価なモデルを選び、Intel On Demandサービスを通じて、必要に応じてアクセラレータ・ライセンスを購入することができる。すべてのチップに同じアクセラレータオプションがあるわけではない。

Intel はまだアクセラレータの価格ガイドを提供していないが、ライセンスはサーバーOEM を通じて提供され、ソフトウェアとライセンスAPI を通じてアクティベートされる。フルライセンスをそのまま購入するのではなく、サービスの使用量を計測する使用量メーターを使った従量制の機能を選ぶこともできる。

Intelオンデマンドサービスの背後にある考え方は、顧客が必要な機能のみを有効化して支払うことを可能にし、同時に新しいサーバーやプロセッサーを購入する必要のない将来のアップグレードパスを提供することである。その代わり、顧客はパフォーマンスを高めるためにアクセラレーションエンジンを採用することを選択することができる。また、Intelとそのパートナーは、同じ機能シリコンから複数の種類のSKUを切り出すことができるため、サプライチェーンの簡素化とコスト削減を実現することができる。

これらの機能は、Intelが長い間プロセッサのダイ上に固定機能アクセラレータを搭載してきた歴史を引き継いだものである。しかし、Sapphire Rapidsに搭載された強力なユニットは、その性能を最大限に引き出すためにソフトウェアによるサポートが必要だ。Intelはすでに複数のソフトウェア・プロバイダと協力し、幅広いアプリケーションでのサポートを実現している。

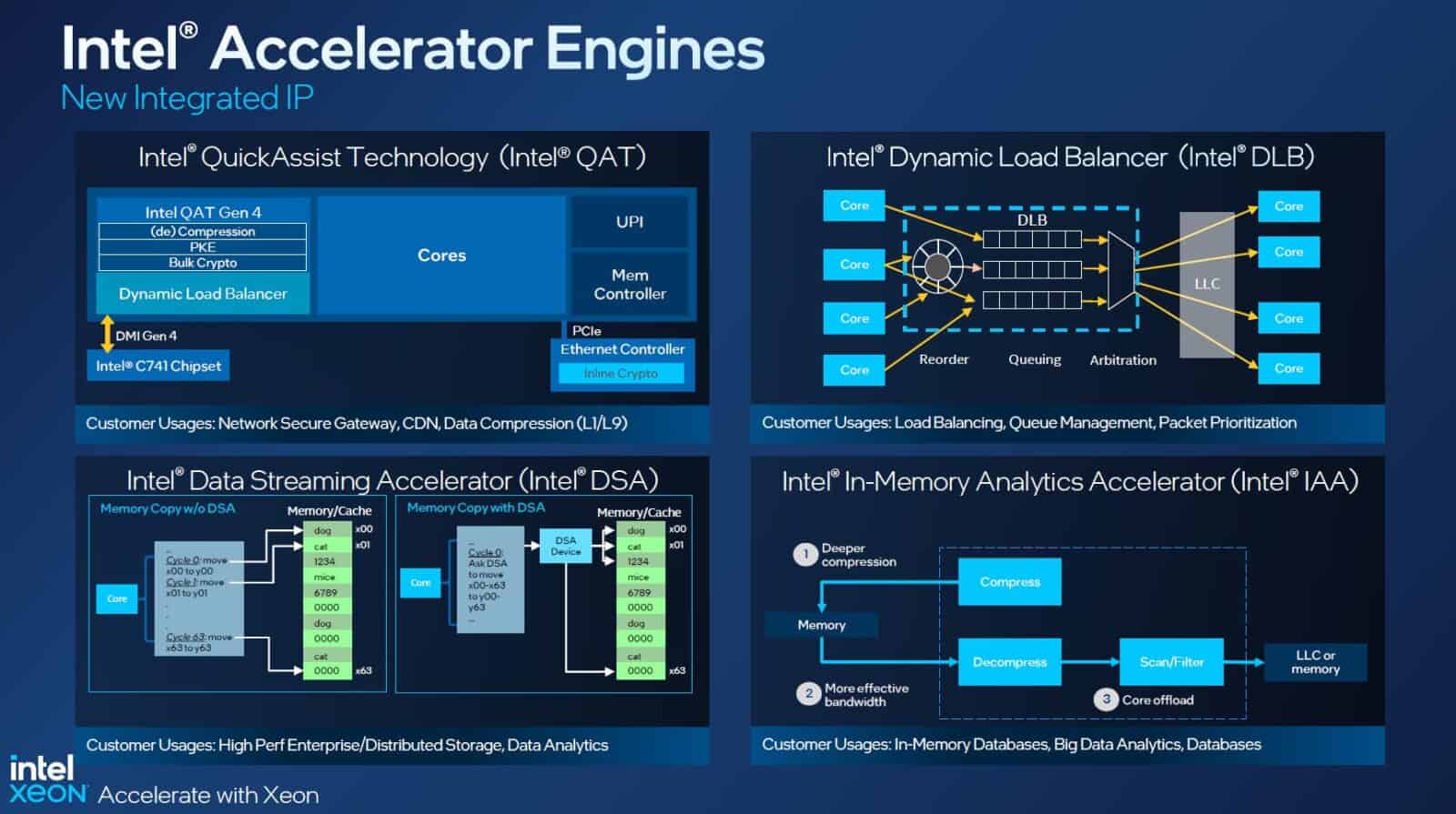

Intelは、Sapphire Rapidsで利用可能な4種類のアクセラレータを用意している。データストリーミングアクセラレータ(DSA)は、データコピーやデータ変換の処理をCPUにオフロードさせることで、データの動きを改善する。DLB(Dynamic Load Balancer)アクセラレータは、パケットの優先順位付けを行い、システム負荷の変動に応じてCPUコア間のネットワークトラフィックのバランスを動的に調整するものである。

また、IAA(In-Memory Analytics Accelerator)は、分析性能を加速し、CPUコアをオフロードすることで、データベースクエリのスループットなどを向上させる。

また、Intelは、Quick Assist Technology(QAT)アクセラレータをCPUに搭載した。この機能は、以前はチップセットに常駐していた。このハードウェアオフロードアクセラレータは、暗号や圧縮・解凍の性能を補強する。Intelはかなり以前からQATアクセラレータを採用しており、この技術はすでに幅広いソフトウェアでサポートされている。

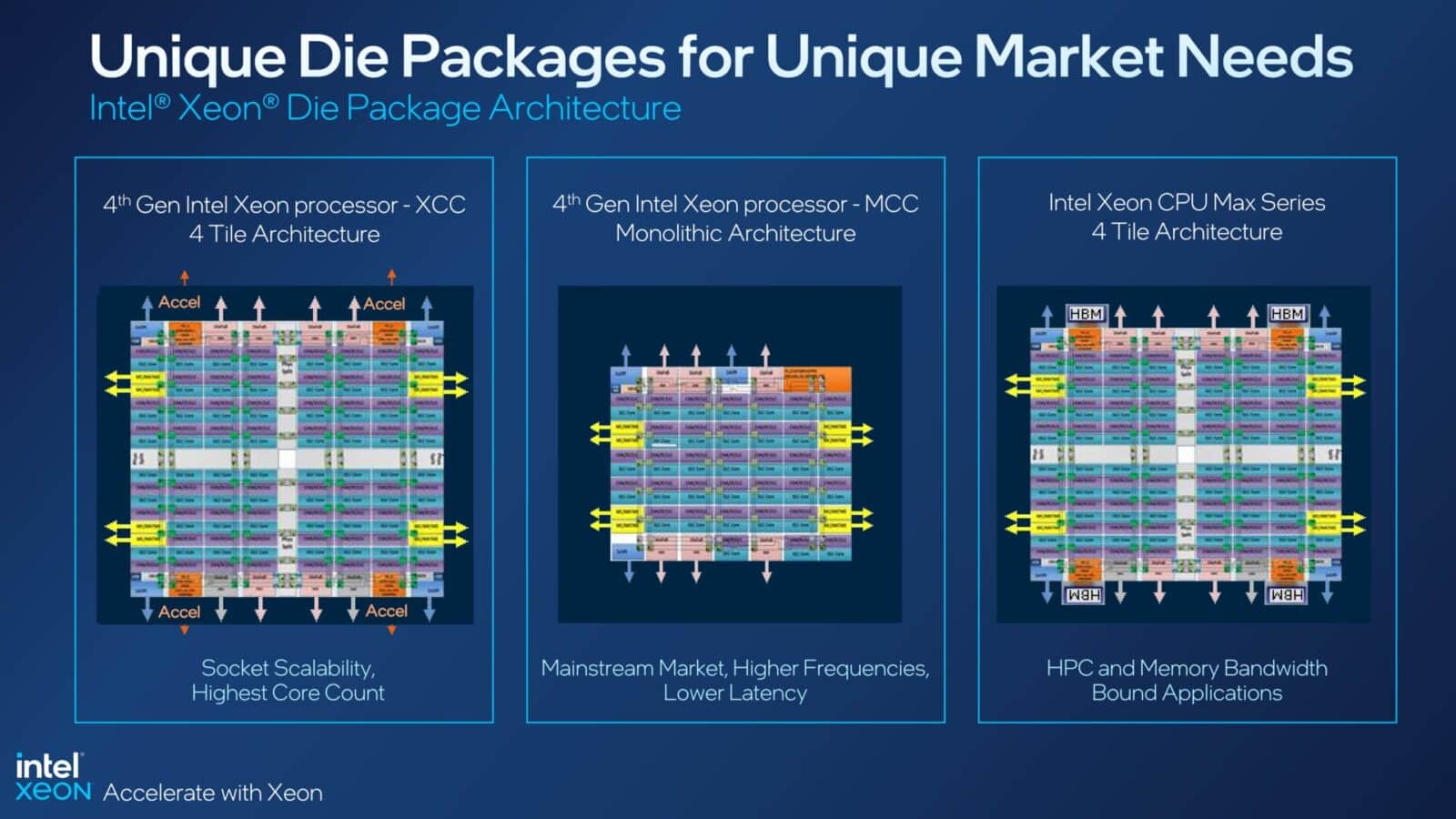

残念ながら、チップのアクセラレーション能力は様々で、すべてのモデルで4つの「デバイス」を購入することはできない。Sapphire Rapidsプロセッサは、SKU表にあるように、2種類の設計(Die Chops)で構成されている。XCCチップは合計4つのダイで構成されており、各ダイには各アクセラレータ(IAA、QAT、DSA、DLB)が1つずつ搭載されている。つまり、これらのチップでは、各タイプのアクセラレータを最大4個まで有効にできる(例えば、IAAを4個、QATを4個、DSAを4個、DLBを4個)。

一方、一部のチップではMCCダイを1個使用しているため、IAAとDSAのアクセラレータは1個、QATとDLBのアクセラレータはそれぞれ2個しか搭載できない(2 QAT, 2 DLB, 1 IAA, 1 DSA)。

Intel Max CPUシリーズとPonte Vecchio Max GPUシリーズ

Intelは先日、近日発売予定のCPU「Xeon Maxシリーズ」と「Intel Data Center GPU Maxシリーズ(Ponte Vecchio)」の詳細を発表したが、本日、正式発表となる。

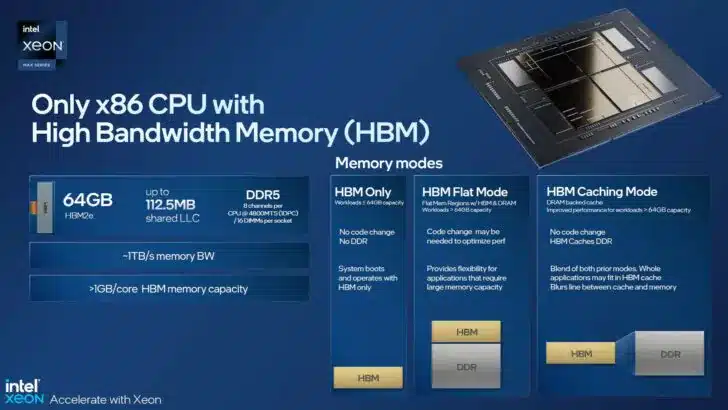

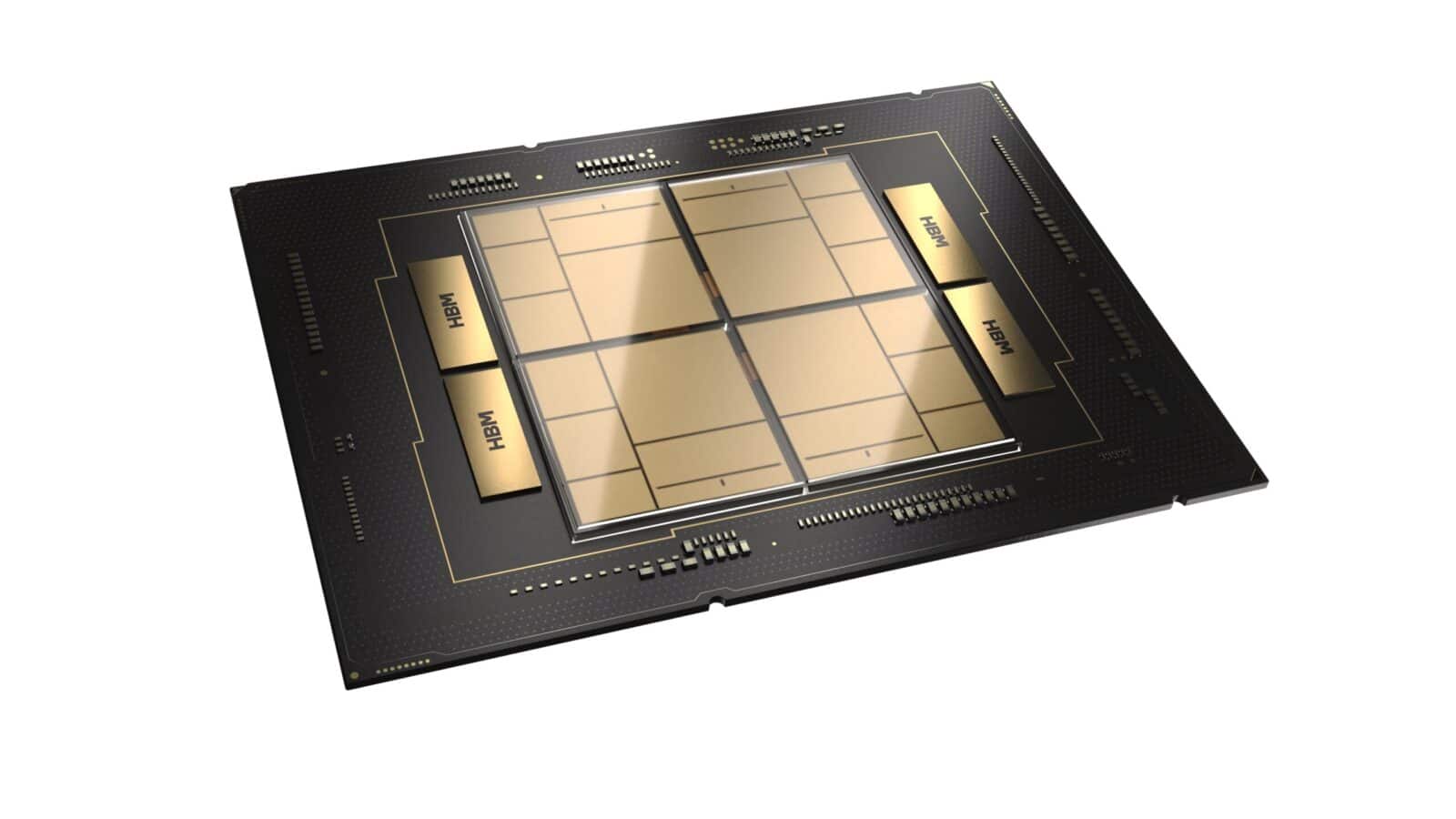

IntelのHBM2e搭載Max CPUは、32~56コアのモデルで、Sapphire Rapidsの標準設計をベースにしている。これらのチップは、オンパッケージでHBM2eメモリを採用した最初のx86プロセッサであり、プロセッサのローカルメモリとしてより大きな64GBのプールを提供する。HBMメモリは、コア数の影響を受けにくいメモリバウンドワークロードに有効であるため、Maxモデルは標準モデルよりもコア数が少なくなっている。対象となるワークロードは、計算流体力学、気候・天気予報、AIのトレーニングと推論、ビッグデータ分析、インメモリデータベース、ストレージアプリケーションなどだ。

Max CPUは、HBMメモリをすべてのメモリ操作に使用した状態(HBMのみ – DDR5メモリは不要)、HBMを別のメモリ領域として提示するHBM「フラットモード」(これには大規模なソフトウェアサポートが必要)、HBM2eをDRAMバックキャッシュとして使用するHBM「キャッシュモード」など、多数のさまざまな構成で動作させることが可能だ。後者はコードの変更が不要で、おそらく最も頻繁に使用される動作モードとなるだろう。

Xeon Max CPUは、3D V-Cacheと呼ばれる3次元積層型L3キャッシュを搭載したAMDのEPYC Milan-Xプロセッサと対決することになる。Milan-Xは、1チップあたり最大768MBのL3キャッシュを搭載し、驚異的な帯域幅を実現しているが、IntelのHBM2eによるアプローチほどの容量は確保できていない。

また、Intelは、これまでコードネーム「Ponte Vecchio」と呼ばれていた「Max GPU Series」を発表した。Intelは以前、標準PCIeとOAMの両方のフォームファクタを持つ3種類のGPUモデルを発表していた。

Sapphire Rapidsの発表の一環として、IntelはOptane Persistent Memory DIMMの最終シリーズを静かに発表した。最終世代はコードネーム「Crow’s Pass」だが、正式には「Intel Optane Persistent Memory 300」と呼ばれ、容量は128GB、256GB、512GBで、DDR5-4400で動作する予定だ。これは、以前のピークであるDDR4-3200よりも大きな改善だが、Sapphire RapidsシステムがOptaneを採用するつもりなら、標準メモリをサポートされているDDR5-4800からDDR5-4400にダウンクロックしなければならないことも意味している。

Intelは、Optane事業終了の理由として、業界がCXLベースのアーキテクチャに移行したことを挙げており、これはIntelの元パートナーのMicronが昨年同事業から撤退した際の心境を反映したものだ。Sapphire Rapidsは、Optane DIMMとCXLインタフェースの両方をサポートしているが、この2つが一緒に見られる最後の機会の1つになるだろう。 CXLは、将来的にチップにエキゾチックメモリを接続するための業界優先方式になると見られている。

Source

コメントを残す