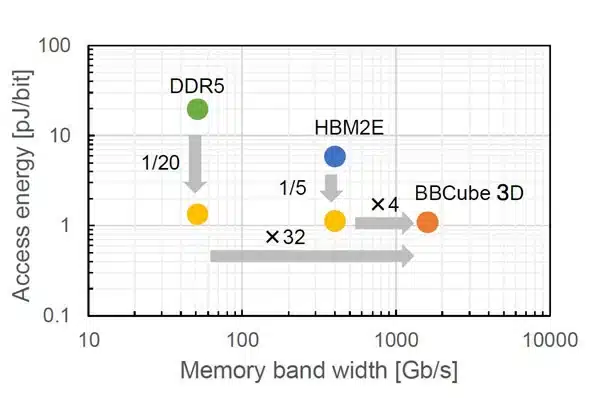

東京工業大学の研究者らは、新しいBBCubeハイブリッド3Dメモリの概要を発表した。BBCube 3Dは「Bumpless Build Cube 3D」の略だ。この新しいタイプのメモリは、プロセッシング・ユニット(GPUやCPUなどのPU)とメモリ・チップ間の帯域幅を改善することで、より高速で効率的なコンピューティングへの道を開くことができるとされている。東工大によると、この技術は、DDR5の30倍、HBM2Eの4倍の帯域幅を提供するという。また、重要な点として、ビットアクセスエネルギーをDDR5メモリの20分の1、HBM2Eの5分の1に削減することで、驚異的な効率を実現していることも驚異的だ。

BBCube 3Dの積層アーキテクチャは、「全世界で達成可能な最高性能を達成した」と東工大のプレスリリースでは述べられている。BBCube 3Dメモリの設計方法を説明する前に、研究者たちは、DDR5やHBM2Eのような現在利用可能なメモリ技術を使用する設計者が直面している問題を概説している。研究者らは、望ましい高帯域幅は現在、高価な広帯域バスか、電力集約的なデータレート向上のいずれか、または両方を犠牲にしていると主張している。

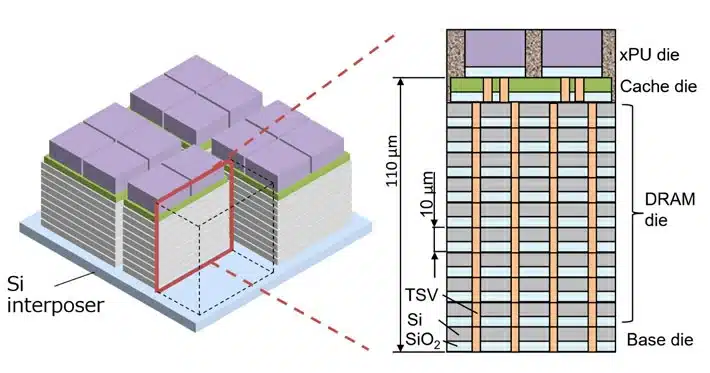

では、BBCube 3DはPUとダイナミック・ランダム・アクセス・メモリー(DRAM)の統合をどのように改善するのだろうか。上の図は、BBCube 3D設計の基本的な概要を示している。Pusがメモリスタックの上にあるキャッシュの上に置かれているのがわかる。これらはすべてシリコンインターポーザーの基盤上に収められている。

さらに、「典型的な、はんだマイクロバンプがなく、長い配線の代わりにTSVを使用しているため、寄生容量が低く、抵抗が低い」と説明されている。この構造は、PUとDRAMを3次元的に接続するもので、前述のシリコン貫通ビア(TSV)を多用している。

東工大が主張するBBCube 3Dの性能は、性能とエネルギー消費の削減という魅力的な組み合わせにより、コンピューティング設計にとって非常に魅力的なものとなるだろう。電力効率に由来するこの設計のもう一つの望ましい品質は、いくつかの3D半導体設計によって引き起こされる可能性のある「熱管理と電源の問題」を軽減することだと言われている。

現在のところ、BBCube 3Dの商業化計画はないようだ。この新技術が “より高速で効率的なコンピューティングへの道を開く”ことを期待したい。

Source

- Tokyo Institute of Technology: BBCube 3D: A Breakthrough in Semiconductor Integration and Data Transmission

コメントを残す