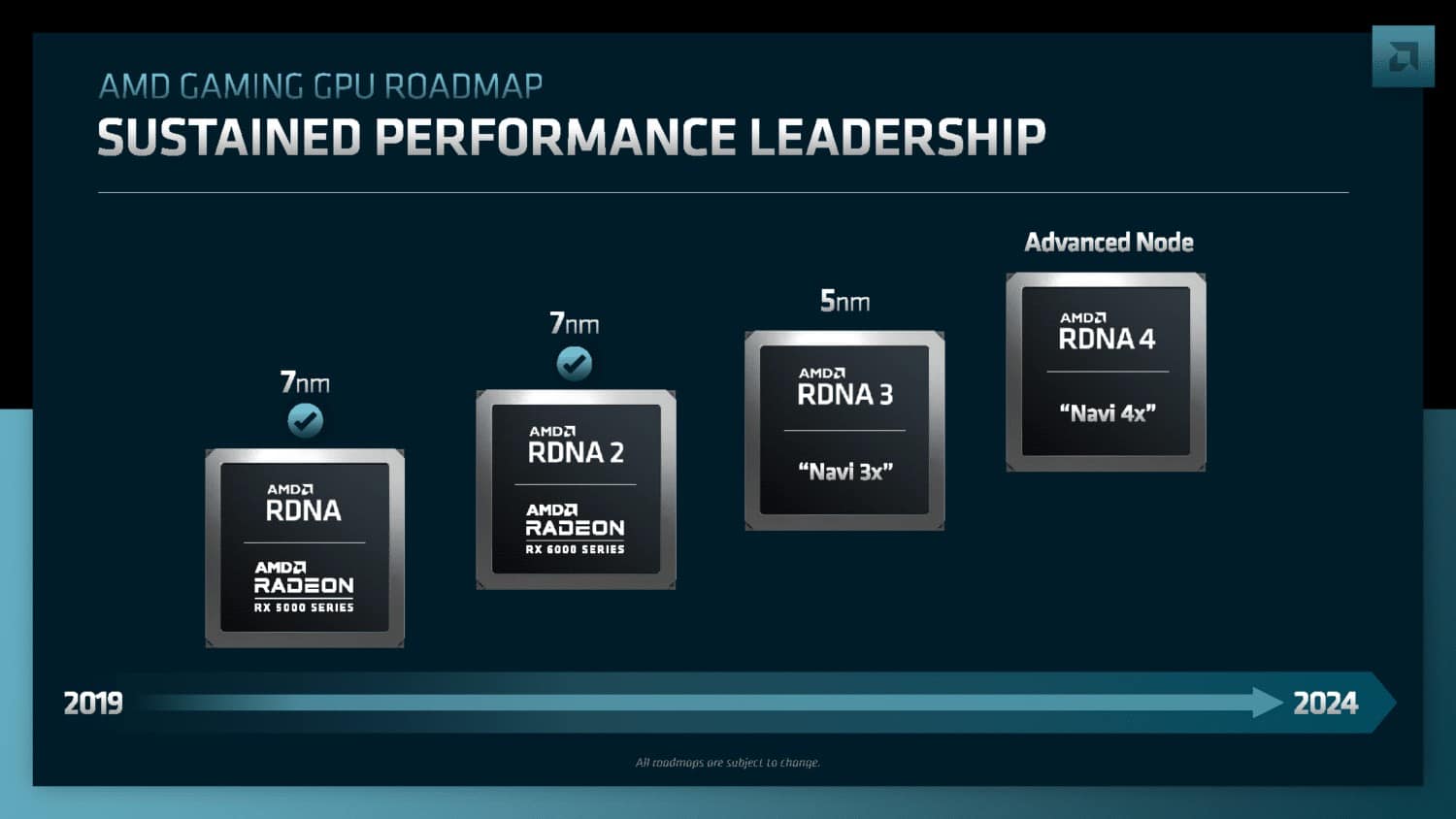

AMDは、アナリスト向けに開催した「Financial Analysts Day」において、新しいGPUロードマップを共有し、2024年登場の「RDNA 4」までのGPUアーキテクチャ及びプロセスノードについて明らかにした。

- AMDは2024年までのGPUアーキテクチャのロードマップを公開した。

- RDNA 3ではワットあたり50%の性能向上を発表

AMD RDNA 4 GPUが2024年に登場

AMDが明らかにしたGPUロードマップによると、新しいNavi 4xのラインナップは、2024年に発売されるとのことだ。具体的なプロセスノードは明らかにされていないが、RDNA 3が5nmであったこと、同様に2024年発売予定のZen 5 CPUが4nmもしくは3nmでの製造と報告されていることや以前の噂から、4nmもしくは3nmでの製造になる物と見られる。

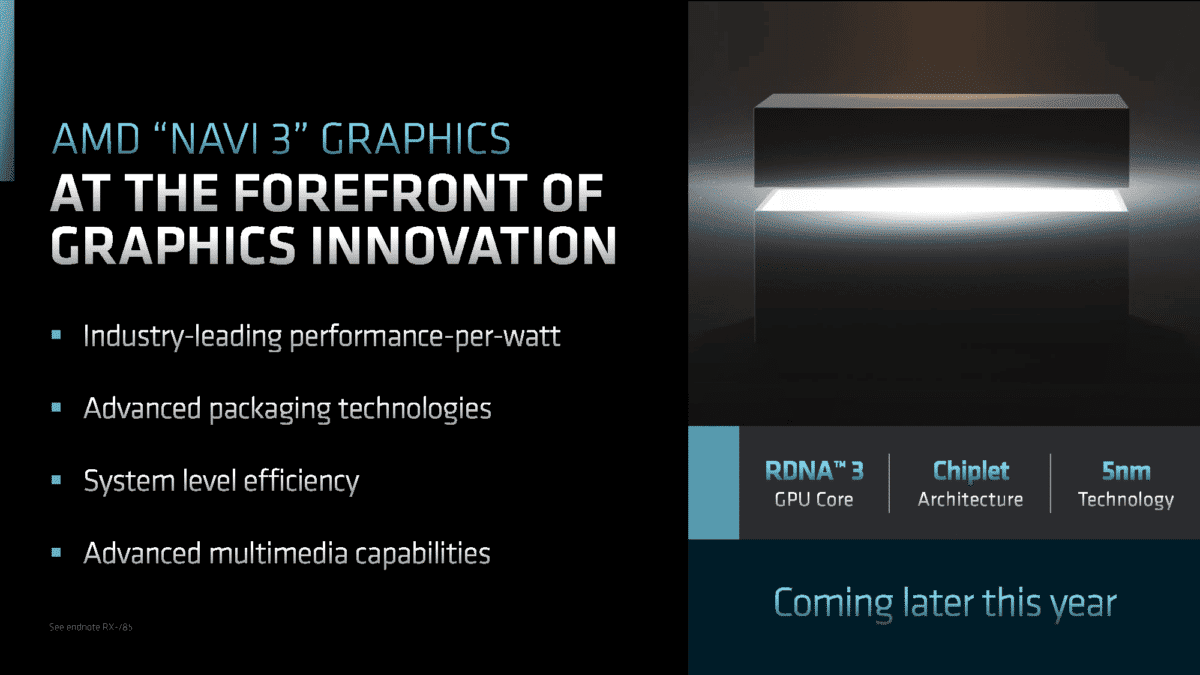

AMD RDNA 3は大幅な性能向上を予告

AMDによれば、RDNA 3はワットあたりの性能を50%以上向上させるとのことだ。ただし、この「ワットあたりの性能が50%上がる」と言う意味は、実際のパフォーマンスが50%上がる訳ではないことには注意が必要だろう。実際に過去にもAMDのRDNA 2アーキテクチャもワットあたりの性能が50%向上したとされており、NVIDIAはAmpereアーキテクチャが以前のTuringアーキテクチャよりもワットあたりの性能が50%向上したと主張していたが、実際のパフォーマンス向上は多くの比較テストで遙かに小さい事が明らかになっている。

AMDが主張する1ワットあたりの性能が50%向上するというのは、一部のテストの最も良かった結果についてであり、その意味はRDNA 3がRDNA 2と同じ電力を使いながら50%高速化するという意味かもしれないし、33%少ない電力で同じ性能になるという意味かもしれない。それについては明らかにされていない。

RDNA 3 のその他の詳細は、すでに噂やリークなどから明らかになっているものばかりだ。

まず、製造は5nm プロセスとなる (恐らくTSMC N5 または N5P) 。そして、AV1エンコード/デコードのサポートなど、「高度なマルチメディア機能」をサポートする予定だ。また、AMDは、RDNA 3が、すでに噂されていたDisplayPort 2.0接続をサポートする事も明らかにしている。

RDNA 3では、AMDのRDNA GPUの主要な構成要素であるコンピュートユニット(CU)について、再設計された物が搭載されることを明らかにした。加えて、AMDは、次世代Infinity Cacheの搭載も明らかにしており、これによって全体的なパフォーマンス向上が期待できそうだ。さらに噂ではAMDは最上位のRDNA 3 GPUをより広いメモリインターフェイス、おそらく384-bitに移行すると言われているが、これについては同社からの言及はなかった。

最後に、RDNA 3で最も興味深い点は、AMDがチップレットアーキテクチャと組み合わせた先進的なパッケージング技術を採用することだろう。これがGPUにとってどのような意味を持つかはまだ未知数だ。

考えられる形としては、メモリインターフェイス、ディスプレイ、メディア機能、およびその他のコアハードウェアを備えたメインハブを持つことだろう。そして、GPUチップレットはローコンピューティングに集中し、Infinity Fabricを通じてルートハブにリンクされます。GPUチップレットは1つから4つまで搭載可能で、豊富な拡張性を提供する。ただし、AMDはこのアプローチで、製品層ごとに複数の異なるルートハブを必要とすると思われ、コストと複雑さが増すことになる。

より可能性が高いのは、AMDがミッドレンジパフォーマンスセグメントをターゲットとするベースGPUチップレットを用意し、このチップレットを高速インターコネクトで2つ、あるいは4つまで連結できるようにすることだろう。SLIやCross Fireのようなものだが、交互にフレームレンダリングする必要はない。OSには、複数のチップレットがあっても1つのGPUしか表示されず、チップレット間のデータ共有はアーキテクチャが担うことになる。。

AMDはすでにAldebaran MI250XデータセンターGPUでこのようなことを行なっており、IntelもXe-HPCデザインで同様のアプローチを取っているようだ。AMDは、データセンター向けCDNA 3 GPUの詳細も明らかにしており、最大で4個のGPUチップレットを搭載することを示唆している。ただし、これらはリアルタイムグラフィックスに特化した設計ではなく、演算に特化したアーキテクチャであるため、乗り越えるべきハードルは異なる。とはいえ、AMDは2017年の最初のCPU「EPYC」以来、複数のチップをパッケージに収めており、2019年のZen 2以降チップレットデザインを採用しているので、チップレットに関する経験は豊富だ。GPUでもこのような設計を実現する方法について、十分な知識を持っているはずだ。

CDNA 3はCPUチップレットを搭載

最後に、AMDはCDNA3アーキテクチャが世界初のエクサスケールAPU設計となることを明らかにした。これは、CPUとGPUのチップレットを1つのパッケージに統合することで実現される。ただし、AMDは、ここでどのCPUチップレットが使われるかは明らかにしていない。この5nmのデータセンター向けGPUアーキテクチャは、来年、Instinct MI300製品シリーズに投入される予定だ。

コメントを残す