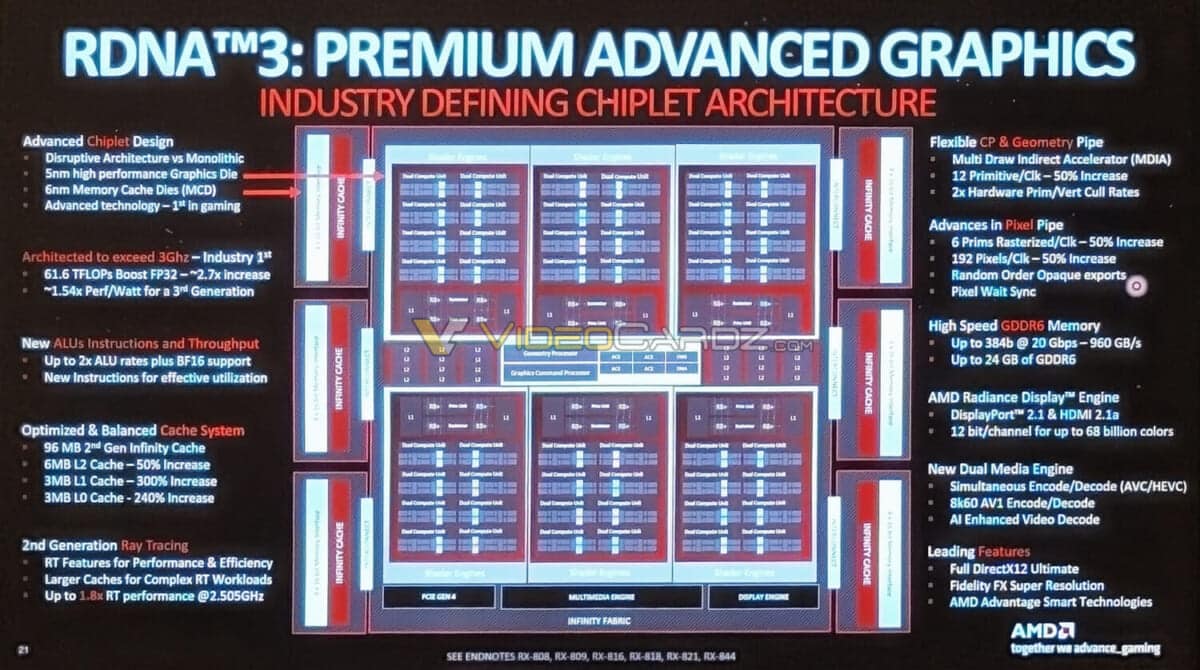

AMD RDNA 3 “Navi 31” GPUのブロック図がリークされ、Radeon RX 7900 XTXおよびRX 7900 XTグラフィックスカードを搭載する世界初のチップレットゲーミングGPUの外観が明らかになった。

VideoCardz: Alleged AMD Navi 31 GPU block diagram leaks out

AMD RDNA 3は、ゲーミングGPUセグメントにおいて、初めてチップレット設計を実現した記念すべき製品となる。元々AMDは、RyzenとEPYC CPUでチップレット革命を起こしたパイオニアであり、その流れをコンシューマ向けGPUにも適用した形だ。AMDによると、チップレットGPU設計は、標準的なモノリシック設計に対して、破壊的なアーキテクチャアプローチを提供するとのことだ。

AMDはこれまで、フルNavi 31 GPUが96MBのL3キャッシュ(別名Infinity Cache)を搭載することを明らかにしていたが、L0、L1、L2キャッシュについては不明だった。それが今回新しくリークされたスライドに記載されている。

- L0 – 3MB – 240%の増加

- L1 – 3MB – 300%の増加

- L2 – 6MB – 50%の増加

- L3 (Infinity Cache) – 96MB (Navi 21より32MB少ない)

ブロック図によると、AMD Navi 31の6つのShader Engineのレイアウトで、それぞれに8つのデュアルCompute Unitを搭載している。AMDは、デュアルイシューSIMDを追加することで演算スループットを2倍にしたが、コア数は2倍になってはいない。そのため、Stream Processorの数は6144だが、実効的な単精度の演算性能は61TFLOPSに向上している。

また、スライドでは、RDNA3アーキテクチャが3GHzを超えることに言及している。これは、実際のリファレンスデザインでは2.5GHzブーストを超えないが、3.0GHzまでスケールアップするアーキテクチャになっているという報道を裏付けるものかもしれない。

キャッシュシステムについては、AMDはRDNA 3 “Navi 31” GPUに合計4つの異なるキャッシュ階層を用意している。まず、Infinity Cache LLCは、5.2TB/sのInfinity Fabricリンクで相互接続された6つのMCDプールで96MBを構成している。L2キャッシュが6MB(50%増)、L1キャッシュが3MB(300%増)、L0キャッシュが3MB(240%増)となっており、L2キャッシュとL0キャッシュの合計で96MBとなる。96MBのInfinity Cacheは、AD102のL3キャッシュとフルにマッチしている。AMDによれば、GPUの実効帯域幅は3.5TB/sである。つまり、Infinity Cacheは約2.5TB/sで、残りの960GB/sはGDDR6インターフェイスからもたらされる。

AMDの第2世代レイトレーシング実装には、より大きなRTアクセラレータが搭載されており、CUあたりの性能が50%向上している。その中には、光線が50%増加し、専用命令、新しいレイボックスのソートとトラバーサルが含まれている。より大きなキャッシュ(複雑なRTワークロードに役立つ)の助けを借りて、AMDは、最大80%のレイトレーシング性能向上(2.5 GHzで)を期待している。

ジオメトリとピクセルパイプラインに目を移すと、AMDはMDIA(Multi-Draw Indirect Accelerator)の利用、12プリミティブ/CLK(50%増)、2倍のハードウェアプリ/ベールカルレートに注目している。ピクセルでは、6 Prims Rasterized/Clk(50%増)、192 Pixels/Clk(50%増)、Random Order Opaque exports、Pixel Wait Syncをアピールしている。あとは、発表会からわかっていることとほぼ同じだ。

革新的な新しいAMD RDNA 3 “Navi 31” GPUは、来月12月13日にコンシューマー向けに発売される。

コメントを残す