NVIDIAは、GPUアクセラレーテッドコンピューティングとAIを組み合わせてチップ設計を改善し、半導体の性能と効率を向上させる新しい方法「AutoDMP(Automated DREAMPlace-based Macro Placement)」を発表した。

インテリアデザイナーが家の中の部屋に椅子やテーブルなどの家具を配置するのと同じように、チップ設計者は、部品間のレイテンシーが重要となる狭い間取りの中で、プロセッサのさまざまなビットやピースをどこに配置するかを考えなければならない。

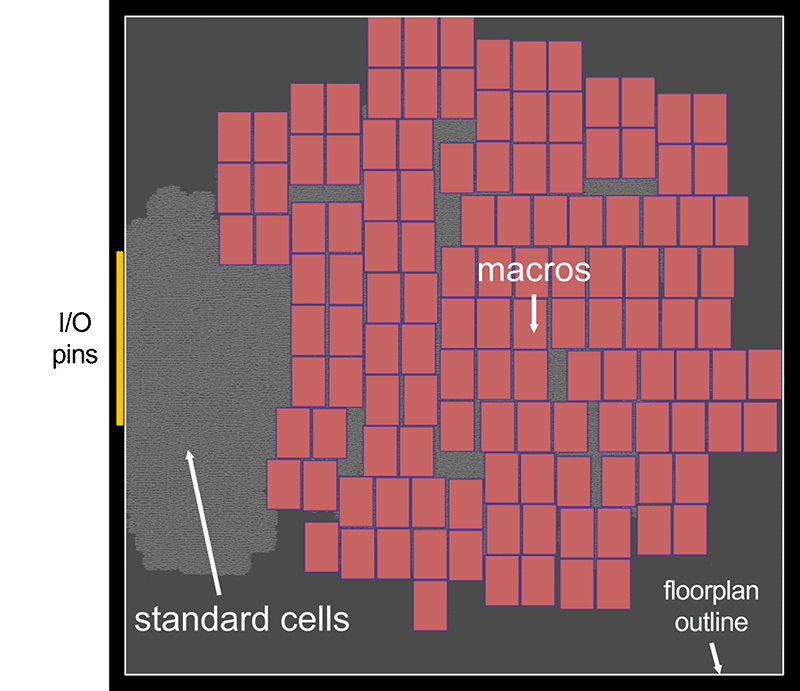

インテリアデザイナーは、部屋の広さや移動のしやすさを考慮しなければならないが、チップ設計者は、半導体デバイスのどこにマクロ(メモリなどのトランジスタブロック、PCI-Expressコントローラやメモリコントローラなどのアナログデバイス、コアそのもの)を配置するかによって、パワー、パフォーマンス、面積がどのように変化するかを考える。

これまでは、まずマクロを配置し、次に小さなスタンダードセルを無数に配置するという2ステップで、非常に手間のかかる作業だった。最近では、マクロとスタンダードセルを同時に配置する、よりミックスされたアプローチも採用されているが、それでも難しいことだ。

「これらのマクロは、デジタル設計の基本的な構成要素であるスタンダードセルよりもはるかに大きいことが多いのです。マクロの配置は、チップの景観に多大な影響を与え、面積や消費電力など、多くの設計指標に直接影響を与えます。したがって、これらのマクロの配置を改善することは、各チップの性能と効率を最適化するために不可欠です。マクロ配置、スタンダードセル配置、そして結果として得られる電力、性能、面積(PPA)の間の現代の複雑な関係を考えると、このプロセスを改善する必要があります」と、NVIDIAの研究者であるAnthony Agnesina氏とMark Ren氏は、彼らが行っているいくつかのAI支援マクロブロック配置作業を説明するブログ投稿で述べている。

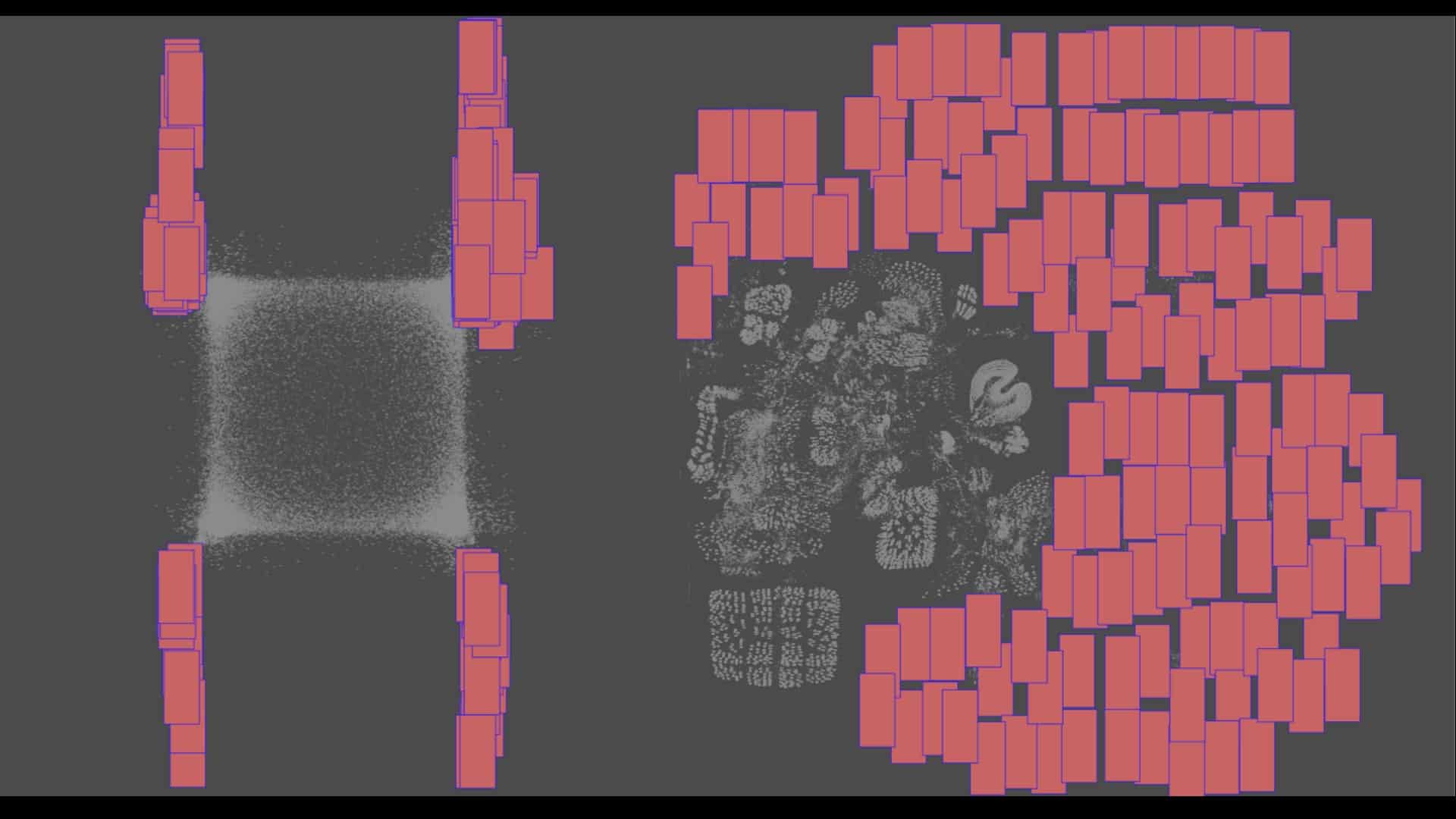

近年、アルゴリズムやニューラルネットワークが多くのマクロ配置例のサンプリングを介して学習する強化学習や、前述のセルとマクロの同時並行といった新しい手法が登場している。NVIDIAは、DREAMPlace(同社が2019年に初めて公開したGPUアクセラレーションによるオープンソースの深層学習ツールキット)を使って、チップ上の超大規模集積回路(VLSI)を配置し、マクロとスタンダードセルを配置するコンカレントな大部分が手作業の方法を改善しようと提案している。

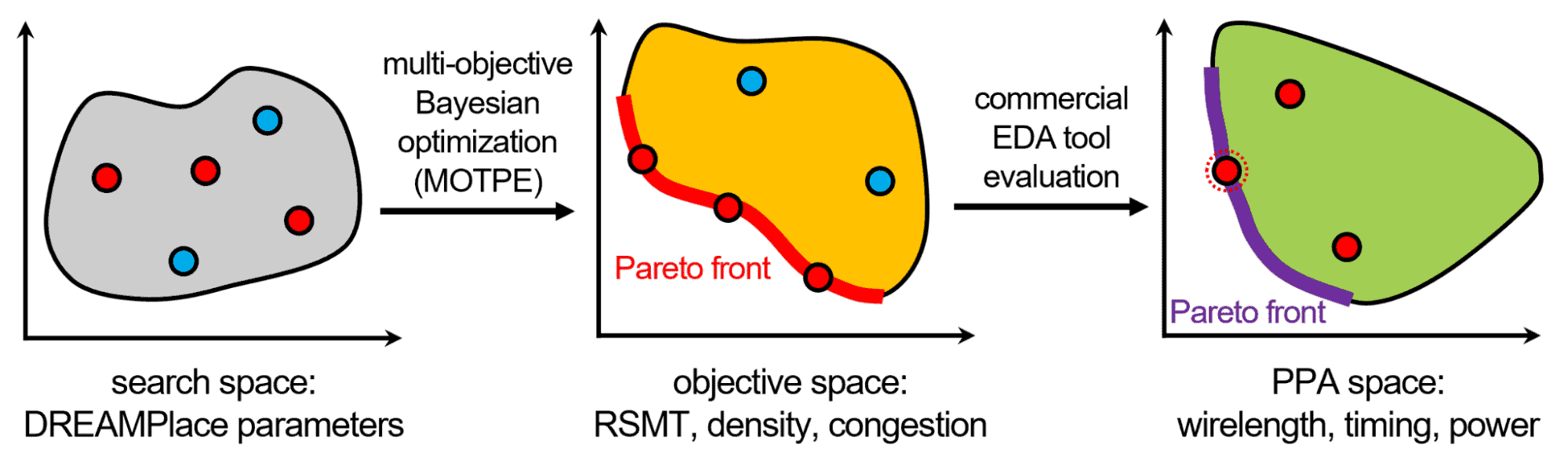

NVIDIAの提案では、現在のセルとマクロの同時配置法の実行方法にも手を加えており、複数オブジェクト最適化のフレームワークを使用して探索空間を拡張し、「最適性ギャップ」(最適解と下界(目的値が下回ることのない値)の差)を減らすことを求めている。

DREAMPlaceは、PyTorch深層学習フレームワークとツールキットを使用して作成された分析的なプレーサーで、配置問題を使用してニューラルネットワークを訓練する。NVIDIAの研究者は今回、AutoDMP(Automated DREAMPlace-based Macro Placement)の研究論文を発表したが、これはGPUメーカーや業界の他の企業が、より強力で効率の良いチップの設計にAIを活用する大きなトレンドの一部と言える。

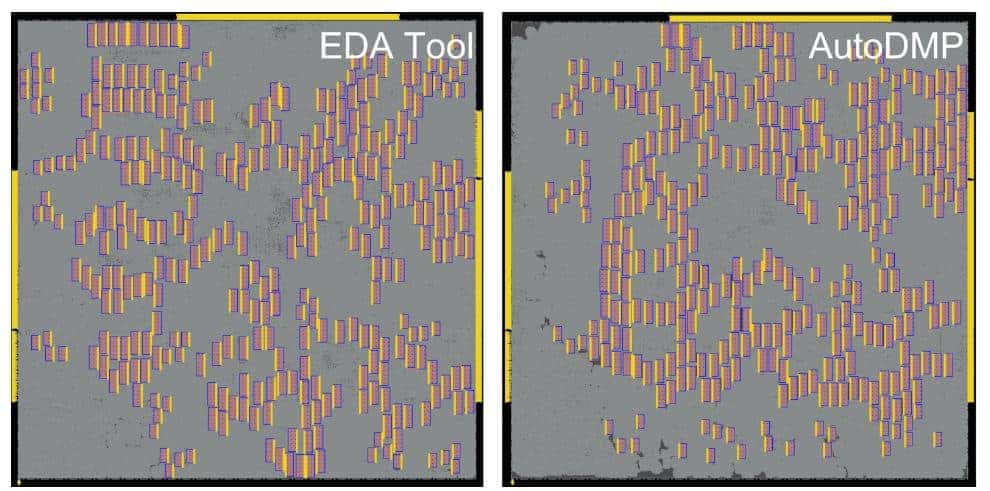

本ソリューションは、PPA(Power-Performance-Area)指標に影響を与えるマクロ配置の問題を解決するために開発された。AutoDMPは、「多目的ハイパーパラメータ最適化技術を用いた自動パラメータチューニングと連動して、マクロとスタンダードセルを同時に配置」することで、高品質の予測可能なソリューションを生成し、学術ベンチマークのマクロ配置品質を向上させることができるとのことだ。

また、NVIDIAはAutoDMPの計算効率について、“NVIDIA DGX Station A100の1台で270万セル、320マクロのデザインを3時間で最適化できる”と述べている。

AutoDMPは、先週開催されたNVIDIAのGTC 2023で、GPUアクセラレーションや機械学習技術から、効率化、電力削減の必要性まで、前面に出ていたすべてのコンポーネントを組み込んでいるという。

「この研究は、MLベースの多目的最適化とGPU加速数値配置ツールを使用して、より良いマクロ配置ソリューションを見つけるために広大なデザイン空間を効率的に探索できることを実証しています。DREAMPlaceは、配置問題を配置密度制約の下でのワイヤ長最適化問題として定式化し、数値的に解決します」と、ブログでは述べられている。

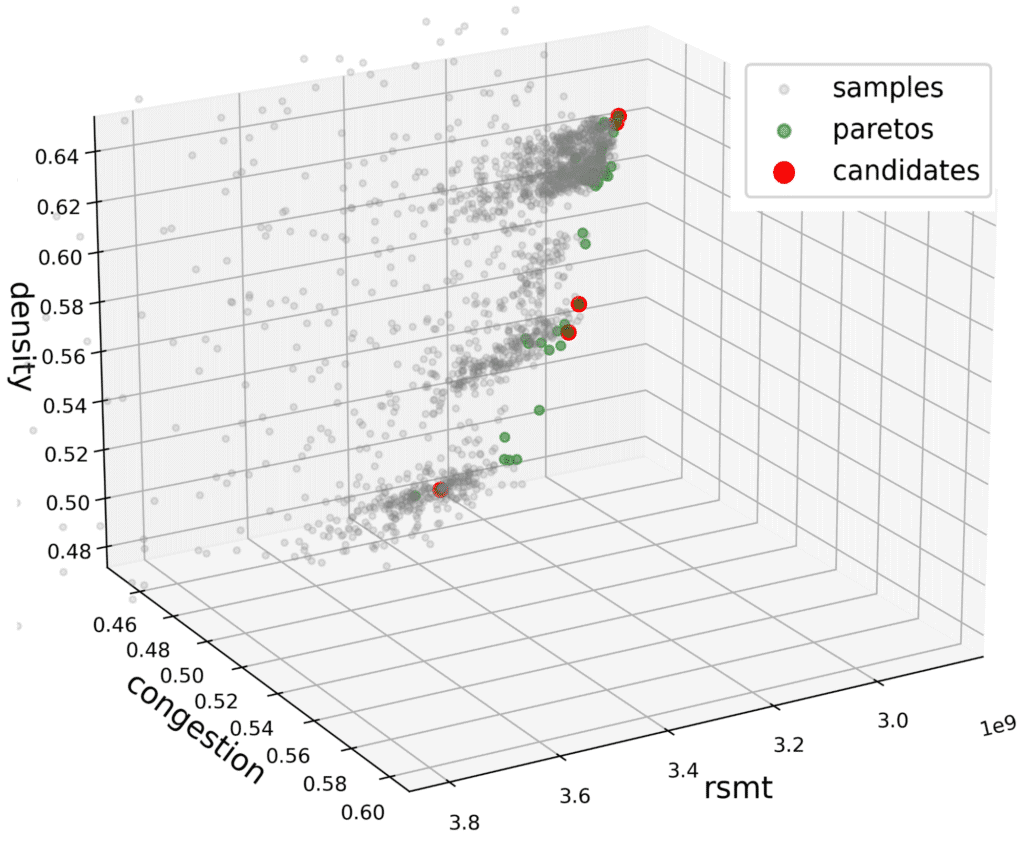

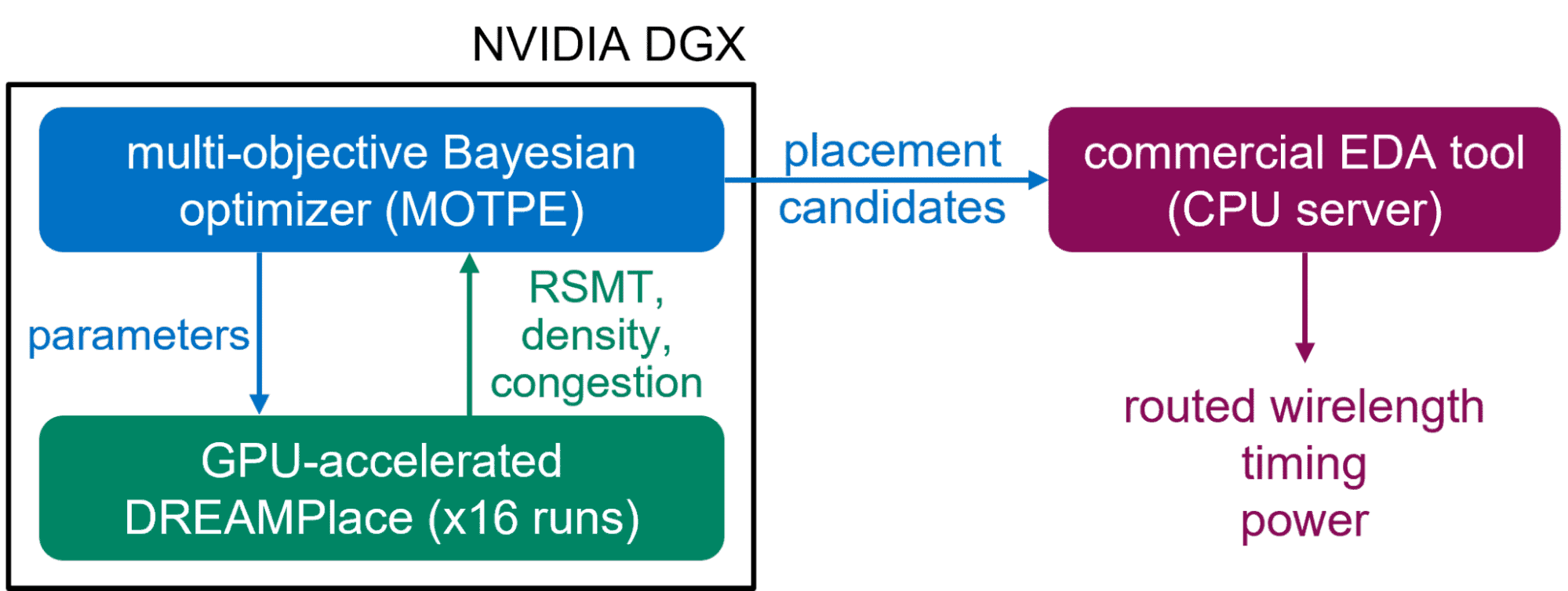

研究者によると、提案手法は、多目的ツリー構造パーゼン推定器(MOTPE)ベイズ最適化アルゴリズムを使用して、線長、セル密度、輻輳に焦点を当てた3つの目的を達成するためにプレーサーのパラメータを調整し、設計空間を探索するものである。探索空間の複雑さを管理するために、2段階の電力、性能、面積(PPA)評価スキームが含まれている。NVIDIAはまた、DREAMPlace配置エンジンの変更を提唱しており、「合法化の問題を軽減し、その設計空間を大幅に拡大し、それによって達成可能なPPAの可能性を高める」としている。

AutoDMPのPPA評価について、同社は次のように説明する。

“まず、AutoDMPの多目的パラメータ最適化により、推定される電線長、混雑度、密度がパレートフロントに位置する配置の集合を見つけることができます。このステップでは、AutoDMPのパラメータの設計空間を、目的プロキシ空間にマッピングします。

次に、目的空間のパレートフロント上のマクロ配置を、EDAツールの実際のPPA空間にマッピングします。EDAツールは配置の最適化を何度も行うため、2つのパレートフロントは一致しない可能性が高く、その多くはヒューリスティックに駆動されるため、予測は非常に困難です。

その結果、目的プロキシ空間のパレートフロントからすべてのマクロ配置でEDAツールを実行し、EDAツールのフロー実行から得られる配線長、タイミング、電力などの実際のPPAメトリックを評価します。”

研究者らは、デザイン空間を定義するためにDREAMPlaceの16個のパラメータを選択し、パラメータは「配置品質に大きく影響するという観察に基づいて決定しました。最適化関連のパラメータ(勾配ベースの数値最適化装置やその学習率など)と物理的なパラメータ(密度評価のためのビン数や密度目標など)が含まれています。多目的最適化は、パレートフロントを見つけようとするものです。これは、少なくとも1つの他の目的を悪化させることなく、どの目的も改善することができない、非主要な目的空間の点の集合です」

また、セルやマクロの位置を平面図の中心に初期設定するなど、DREAMPlaceのパラメータを超えるパラメータを追加し、最終的な配置のクオリティに影響を与えるようにした。また、マクロの合法化(マクロが重ならず、さまざまな設計上の制約に沿うように配置すること)を容易にするため、マクロ間の縦と横の最小間隔を確保する2つのパラメーターを追加した。

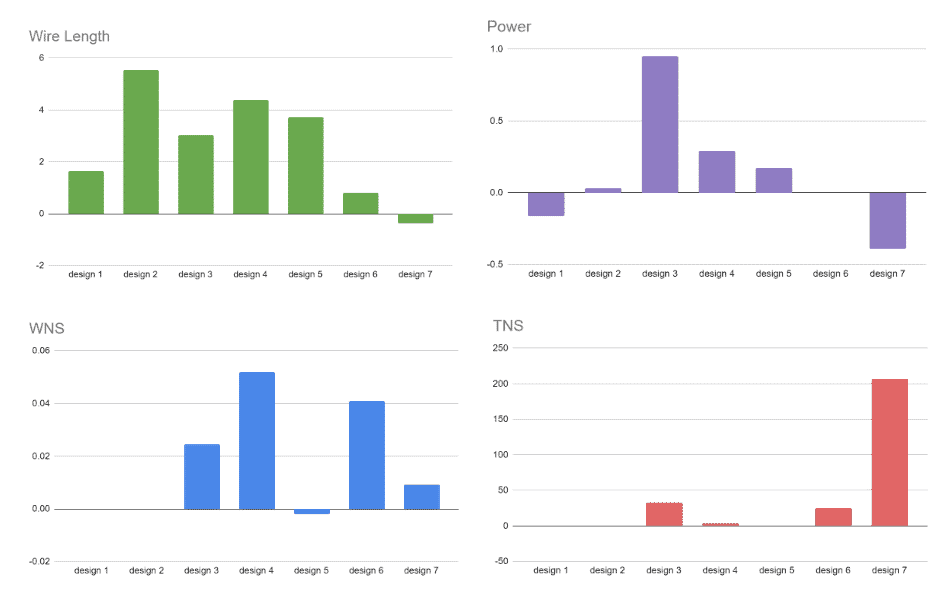

AutoDMPは、TILOS AI-Instituteが提供するマクロ配置ベンチマークを使用して評価された。このベンチマークには、多数のマクロを搭載したCPUやAIアクセラレータの設計が含まれている。評価では、AutoDMPを市販のEDAツールと統合し、Nvidia DGX AIシステムで多目的最適化を実行した。このシステムには、それぞれ80GBの高帯域幅メモリを搭載した4つの「Ampere」A100 GPUアクセラレータが含まれている。16の並列プロセスを起動し、パラメーターのサンプリングとDREAMPlaceの実行を行い、選択した配置をCPU搭載サーバーで動作するTILOSのEDAフローで実行した。

DREAMPlaceの拡張パラメータを調整し、多目的最適化を行うことで、研究者は、DGXシステムで数時間以内にマクロ配置オプションを生成することができたと書いている(各デザインについて1000のデザインポイントをサンプリングすることが含まれます)。さらに、「この進歩により、初期段階の建築探査の納期を短縮し、間取り変更の決定をより正確かつ効率的に評価できます」と付け加えている。

「この研究は、GPU加速プラサーとAI/ML多目的パラメータ最適化を組み合わせることの有効性を実証しています。さらに、現代のチップ設計フローにおけるスケーラビリティの重要性を考えると、この方法論が新たな見込みのある設計空間探索技術を解き放つことができると期待しています」

論文

参考文献

- NVIDIA: AutoDMP Optimizes Macro Placement for Chip Design with AI and GPUs

- via Tom’s Hardware: Nvidia Tech Uses AI to Optimize Chip Designs up to 30X Faster

研究の要旨

超大規模集積回路(VLSI)の配置は、設計完了のための最も重要なステップの1つである。本論文では、解析的な配置問題をニューラルネットワークの訓練に等価にキャストすることにより、新しいGPU加速配置フレームワークDREAMPlaceを提案する。DREAMPlaceは、広く採用されている深層学習ツールキットPyTorchの上に実装され、配線長と密度の計算のためにカスタマイズされたキーカーネルを用いて、最先端のマルチスレッド配置器RePlAceと比較して、品質劣化なしにグローバル配置で30倍以上の高速化を達成することが出来る。私たちは、この研究成果によって AIハードウェア・ソフトウェアの進歩に伴い、EDAの古典的な問題を見直す新たな方向性を提示する。

コメントを残す