Seul Economyを引用したDigiTimesの報道によると、高帯域幅メモリ(HBM)の次世代版「HBM4」は最大2048ビットのメモリ帯域幅に達する可能性があり、GPUとAIセグメントに計り知れない可能性を開く可能性があるとの事だ。

HBM史上初のメモリ帯域幅向上か

HBM1は、スタックあたり最大128GB/秒の速度しか出せないという、やや制限のあるものだった。HBM1を使用するグラフィックカードは、物理的な制限のため、メモリの上限が4GBだった。しかし、SK hynixやSamsungなどのHBMメーカーは、時間の経過とともにHBMの欠点を改善してきた。

HBM2は、潜在的な速度をスタックあたり256GB/秒に、最大容量を8GBに倍増させた。2018年、HBM2はHBM2Eと呼ばれるマイナーアップデートを受け、容量の上限が24GBにさらに増加し、さらなる速度向上がもたらされ、最終的にピーク時にはチップあたり460GB/秒に達した。

HBM3が登場すると、速度は再び倍増し、スタックあたり最大819GB/秒を実現した。さらに印象的なのは、容量が24GBから64GBへと約3倍に増加したことだ。HBM2Eと同様、HBM3でもHBM3Eという世代途中でアップグレードが行われ、理論速度はスタックあたり最大1.2TB/秒まで向上した。

その過程で、HBMはコンシューマーグレードのグラフィックカードにおいて、より手頃な価格のGDDRメモリに徐々に取って代わられるようになった。HBMはデータセンターの標準となり、ワークプレイス向けカードのメーカーはより高速なインターフェイスの使用を選択した。

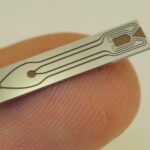

ただし、さまざまなアップデートや改良を経る中で、HBMはそのすべてにおいて同じ1024ビット(スタックあたり)インターフェイスを維持してきた。DigiTimesからの報告によると、HBM4では、これがついに変わるかもしれない。その主張が真実であれば、メモリ帯域幅は1024ビットから2048ビットに倍増することになる。

メモリメーカーが、HBM3Eスタックでサポートされている~9GT/秒のデータ転送速度を、2048ビットインターフェースのHBM4スタックで維持できるかどうかは不明だが、もし可能であれば、バス幅の拡大により、ピーク帯域幅はスタックあたり1.15TB/秒から2.30TB/秒に倍増することになる。また、より高いメモリ・インターフェースは、メーカーがカード内で使用するスタックの数を減らすことを可能にする。スタックあたりのメモリ・インターフェースの幅が広がることで、プロセッサーとインターポーザーが扱うスタック数にどのような影響が出るかは不明だ。

たとえば、NVIDIAのフラッグシップ AI カード「H100」は現在、1024ビットの既知の良品スタックダイを6個使用しており、これにより 6144ビットのインターフェイスを実現している。メモリインターフェイスが2倍の2048ビットになれば、NVIDIAは理論上、ダイの数を3つに減らしても同じ性能を得ることができる。もちろん、HBM4が量産されるのは数年先であることはほぼ確実であるため、メーカーがどの道を選ぶかは不明である。

SK hynixもSamsungも、HBM4の製造を開始すれば「歩留まり100%」を達成できると考えている。

Sources

- DigiTimes: Samsung and SK Hynix building 2,000 I/O ports on HBM4

- via Tom’s Hardware: HBM4 2048-Bit Memory Could Dramatically Increase Bandwidth: Report

コメントを残す