現在、AIの進歩スピードには目を見張る物がある。この急激なスピードには、人間自身が追いついていないとして、規制を巡る動きが活発になって来ているが、それでも電気・コンピュータ工学のUSC教授であるJoshua Yangは、ハードウェアが既に進歩の「ボトルネック」になっていると述べている。彼らは、携帯デバイスにおけるAIのためのこれまでに開発された最高のメモリを持つ新しいタイプのチップを開発したと考えている。

過去約30年間、AIおよびデータサイエンスのアプリケーションに必要なニューラルネットワークのサイズが3.5ヶ月ごとに倍増してきた一方、それらを処理するために必要なハードウェアの能力は3.5年ごとに倍増してきた。

Yang氏によると、ハードウェアのボトルネックは非常に深刻な問題であり、政府、産業界、学界は、このハードウェアの課題に取り組んでいる。シリコンチップによるハードウェアソリューションに取り組んでいる人々もいれば、新しい材料やデバイスを試験する人々もいる。Yang氏らの研究は、新しい材料と従来のシリコンテクノロジーの利点を結合することに焦点を当て、重いAIおよびデータサイエンスの計算をサポートできるようにすることを目的としている。

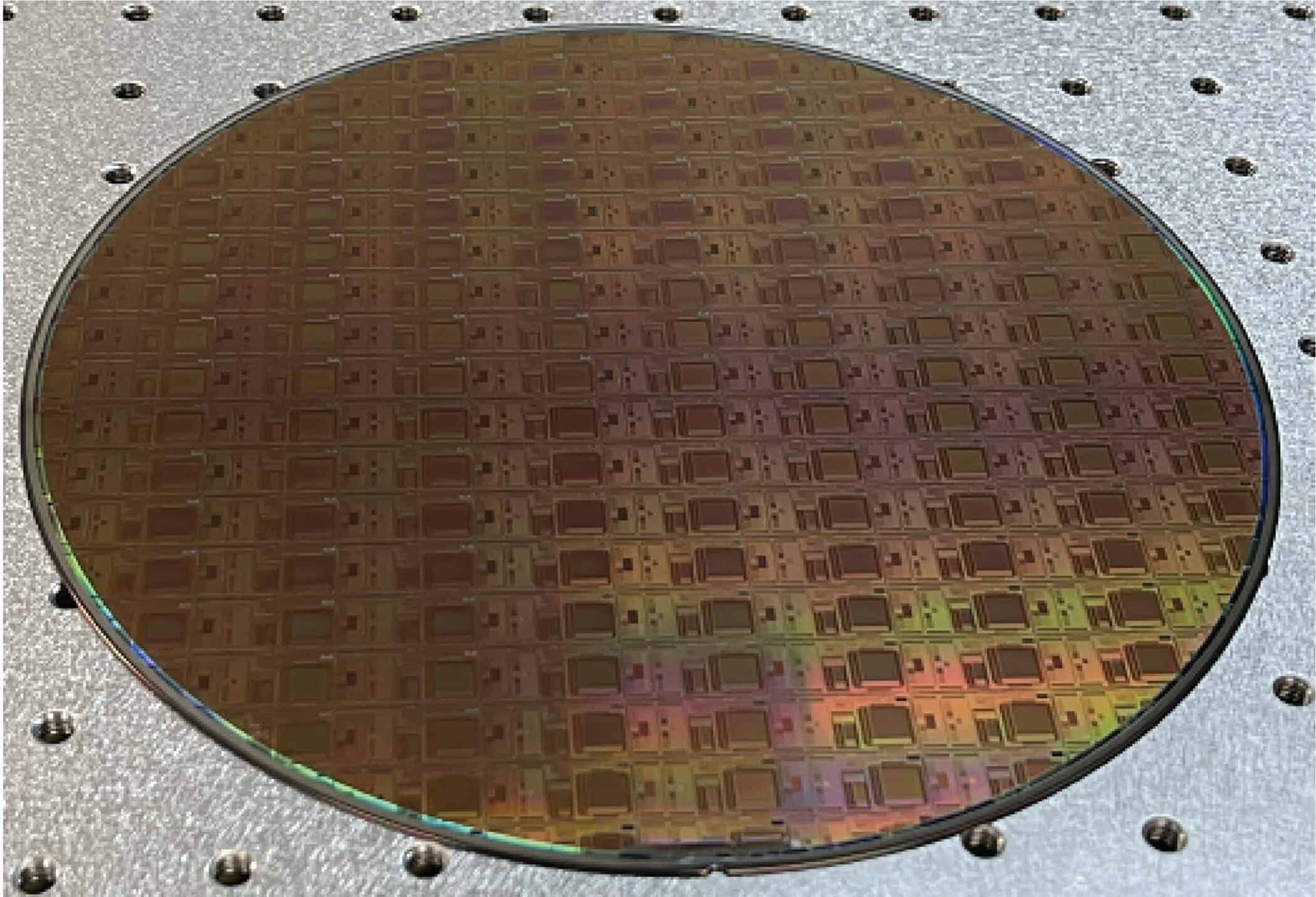

研究チームは、AIハードウェアに必要なドラスティックなメモリ容量の増加につながる基礎物理学の理解に焦点を当てた新しい研究を、『Nature』誌に発表した。Yang氏率いるチームは、USC(Han Wangグループを含む)、MIT、およびマサチューセッツ大学の研究者らが協力して、ノイズを減らすためのデバイスのプロトコルを開発し、統合チップでこのプロトコルの実用性を実証した。このデモンストレーションは、AI加速技術を商品化するためにYang氏と共同著者のMiao Hu、Qiangfei Xia、Glenn Geと共同創業したスタートアップ企業のTetraMemで行われた。

Yang氏によると、この新しいメモリチップは、これまでに知られているすべての種類のメモリ技術の中で、デバイスあたりの情報密度が、最高になっている(11ビット)とのことだ。これらの小さくて強力なデバイスは、ポケットのデバイスに驚くほどのパワーをもたらす上で重要な役割を果たすことを可能とする。これらのチップはメモリだけでなくプロセッサでもあり、多数のチップが小さなチップに集積され、AIタスクを並列で高速に実行するために小さなバッテリーだけで動作する可能性がある。

Yang氏と彼の同僚が作成しているチップは、シリコンと金属酸化物メモリストルを組み合わせて強力でありながら低エネルギー集約型のチップを作り出すものだ。この技術は、チップ上での計算に関わる現在の技術である電子の数ではなく、原子の位置を使用して情報を表現することに焦点を当てている。原子の位置は、デジタルではなくアナログでより多くの情報をコンパクトかつ安定して保存する方法を提供する。さらに、情報は専用の「プロセッサ」の一つに送信されることなく、保存されている場所で処理されるため、現在のコンピューティングシステムに存在する「フォン・ノイマン・ボトルネック」を排除することができる。これにより、Yang氏によれば、AIのためのコンピューティングは「よりエネルギー効率が高く、スループットが高くなる」と言える。

Yang氏は、従来のチップで操作される電子は “軽い”と説明する。この軽さが、動き回りやすく、不安定になりやすい原因だ。Yang氏と共同研究者たちは、電子で情報を保存する代わりに、完全な原子での情報保存をしているのだ。

この方法では、格納された情報を維持するためにバッテリー電源は必要ない。AI計算でも同様のシナリオが発生し、高情報密度の安定したメモリが重要だ。この方法により、「情報密度を高めるために多数のメモリレベルを提供できる」。この新しい技術により、Googleグラスなどのエッジデバイスに強力なAI機能を実現することができるかもしれないとYang氏は想像している。

現在、ChatGPTはクラウド上で実行されている。新しいイノベーションによって、さらなる開発に続いて、個人用デバイスにミニバージョンのChatGPTを搭載する事が、将来のデバイスでは可能になるかもしれない。高性能なテクノロジーをより手頃な価格で、様々なアプリケーションでよりアクセス可能にすることができる可能性があるだろう。

論文

参考文献

- Nature: Memristor devices denoised to achieve thousands of conductance levels

- EurekAlert!: New chip design to provide greatest precision in memory to date

研究の要旨

メモリスティブデバイスを用いたニューラルネットワークは、機械学習や人工知能6、特にエッジアプリケーションにおけるスループットとエネルギー効率の向上に寄与できる能力を有している。ニューラルネットワークモデルをゼロからトレーニングすることは、ハードウェアリソース、時間、エネルギーの点でコストがかかるため、エッジに分散している何十億ものメモリスティックニューラルネットワークに対して個別に行うことは非現実的である。現実的な方法としては、クラウドトレーニングで得られたシナプス重みをダウンロードし、エッジアプリケーションの製品化のために直接メムリスタにプログラムすることであろう。特定の状況に適応させるために、ミムリスタのコンダクタンスに何らかのポストチューニングを行った後、またはアプリケーション中に行うことができる。したがって、ニューラルネットワークアプリケーションでは、多数のメムリスティックネットワークで均一かつ正確な性能を保証するために、メムリスタには高精度のプログラム性が求められる。そのためには、実験室で作られたデバイスだけでなく、工場で製造されたデバイスも含めて、各メムリスタデバイスに多くの区別可能なコンダクタンスレベルが必要だ。多くのコンダクタンス状態を持つアナログメモリスターは、ニューラルネットワークのトレーニング、科学的コンピューティング、さらには「死せるコンピューティング」など、他のアプリケーションにも役立つ。ここでは、市販のファウンドリでCMOS(相補型金属酸化膜半導体)回路上に256×256のメモリスタアレイをモノリシックに集積したチップにおいて、メモリスタが達成した2048個のコンダクタンスレベルを報告する。また、このような制約を回避するための電気的動作プロトコルを開発し、従来ミミスターで実現可能なコンダクタンスレベルの数を制限していた基礎物理を明らかにした。これらの成果は、メムリスティックスイッチングの微視的な姿の基本的な理解だけでなく、さまざまな用途に向けた高精度なメムリスタを実現するためのアプローチにつながるものだ。

コメントを残す