AMDは先月末にRyzen 9 7950X3Dを発表し、16コアCPUでの有用性についていくつかの意見が分かれたものの、第2世代の3D V-Cacheは大きく歓迎されている。今回、その性能を説明する技術的な詳細が2023年International Solid-State Circuits Conference (ISSCC)にて明らかにされた。

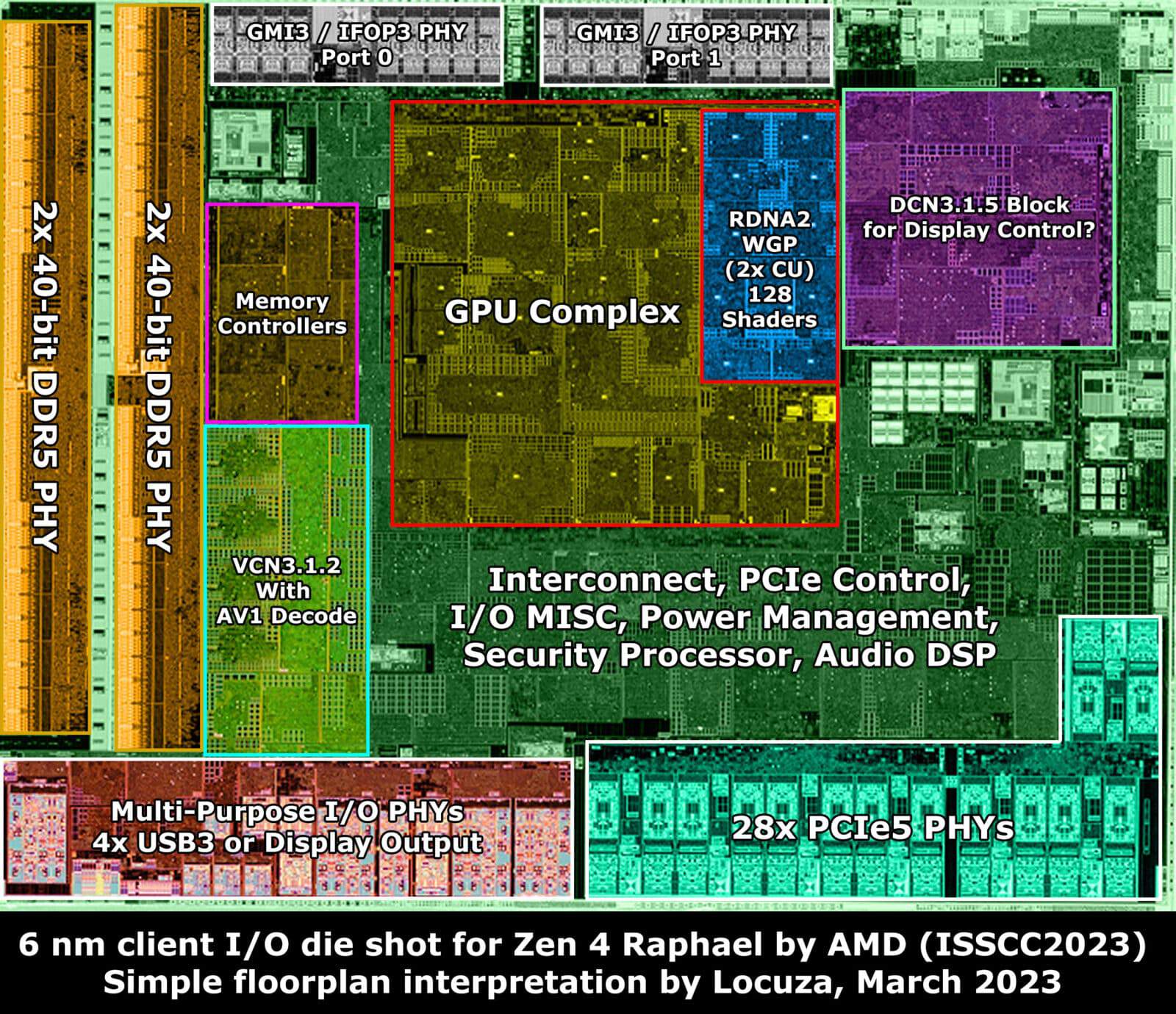

AMDは、2019年にZen 2マイクロアーキテクチャのCore Complex Die(CCD)に7nmノードを、IOダイに12nmノードを採用し、ノードの混在を始めた。AMDは最近、Tom’s Hardwareに、Zen 4ではそれをCCD用の5nmノード、IOダイ用の6nmノード、V-Cache用の7nmノードの3ノードにステップアップさせることを確認していた。

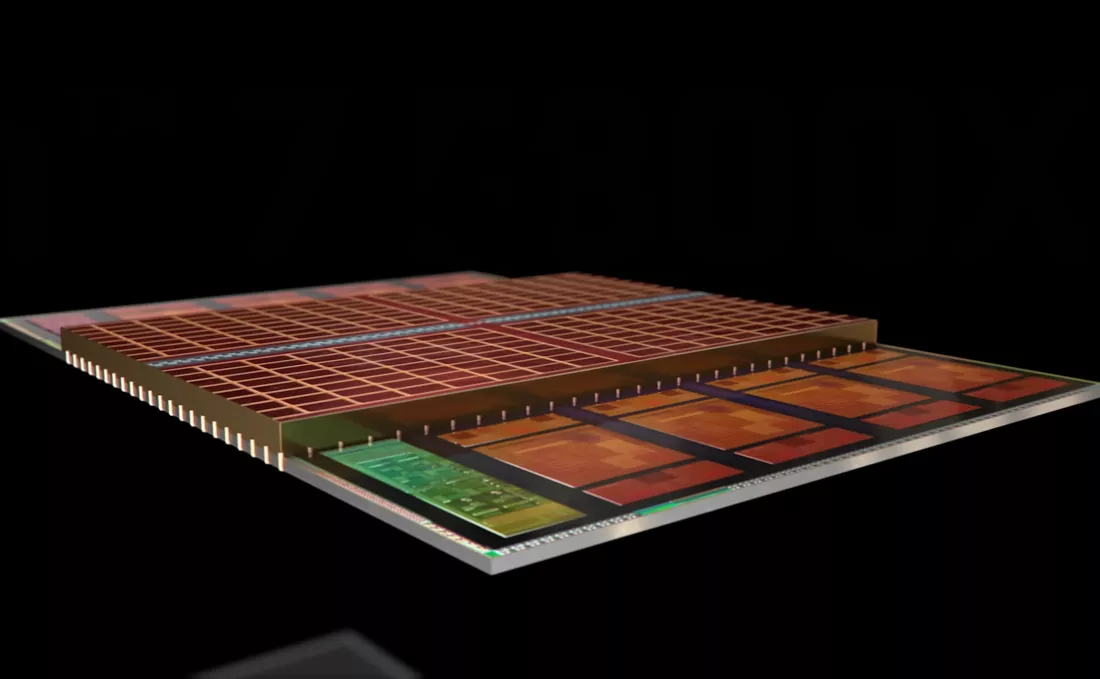

ISSCCのプレゼンテーションでAMDは、1つのノードを別のノードに積み重ねる際に直面した課題のいくつかを説明した。7950X3Dとオリジナルの5800X3Dは、V-Cacheを通常のL3キャッシュの上に配置し、接続できるようにしている。この配置は、V-Cacheをコアの発熱から遠ざけることにもなる。しかし、5800X3DではV-CacheがL3キャッシュの上にきれいに収まっているのに対し、7950X3Dではコアの端にあるL2キャッシュと重なっている。

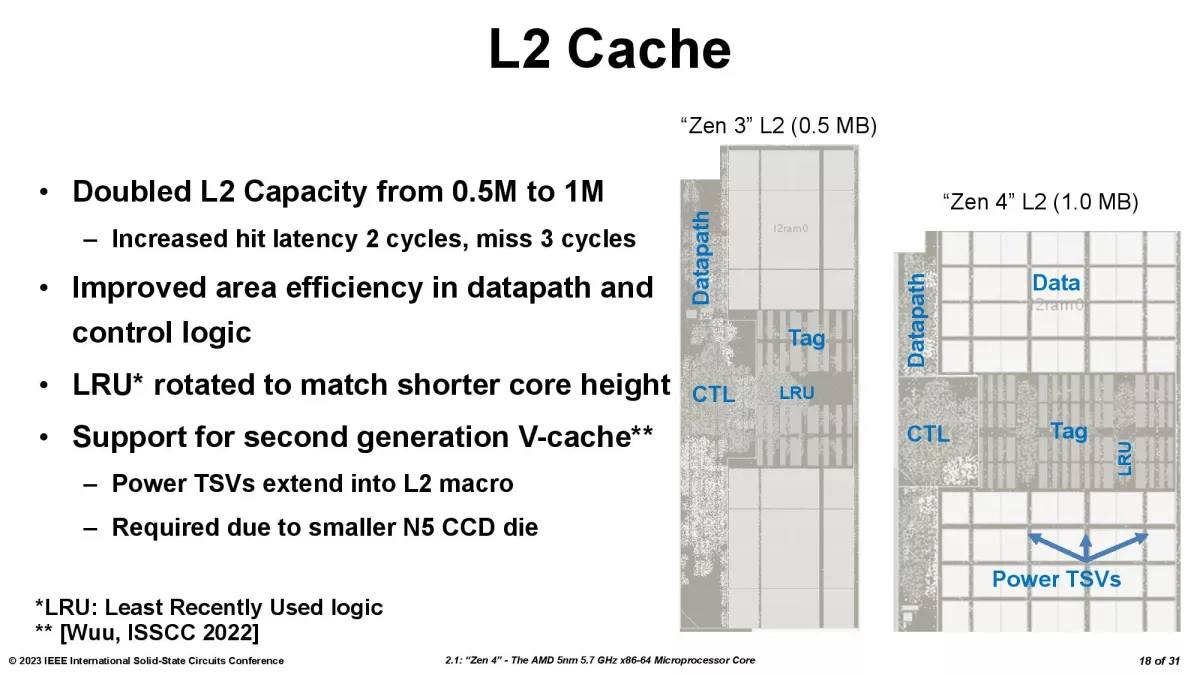

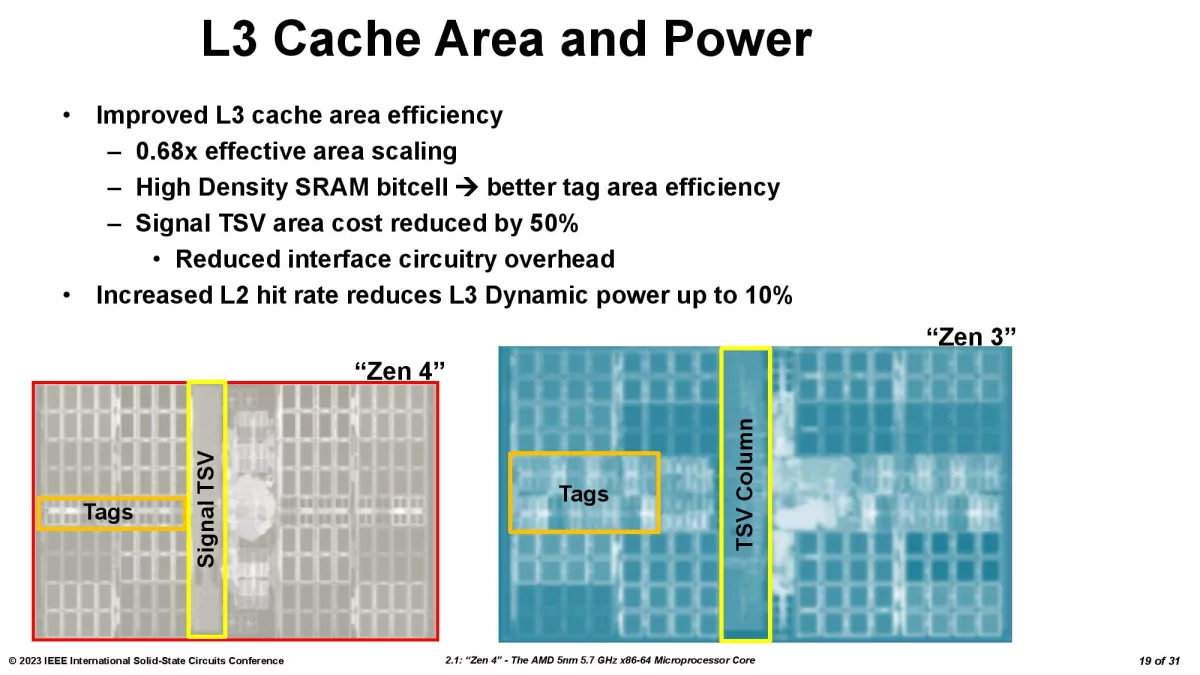

問題の一つは、AMDが各コアのL2キャッシュをZen 3の0.5MBからZen 4の1MBに倍増させたことだが、Vキャッシュに電力を供給するシリコン貫通ビア(TSV)用にL2キャッシュに穴を開けることでスペース上の制約を回避しているとのことだ。信号用TSVは、依然としてCCDの中央にあるコントローラーから供給されているが、AMDはこのTSVにも手を加えて、フットプリントを50%削減した。

AMDはV-Cacheを41mm2から36mm2に縮小したが、同じ4.7Bトランジスタを維持した。TSMCは、SRAM用に特別に開発した7nmノードの新バージョンでキャッシュを製造している。その結果、CCDがはるかに小さい5nmノードで製造されているにもかかわらず、V-CacheはCCDよりも1平方ミリメートル当たり32%多いトランジスタを搭載している。

AMDが実施した改良と回避策をすべて合わせると、帯域幅は25%増の2.5TB/秒になり、効率も不特定多数に向上している。補足的なチップレットの第1世代と第2世代の間が9カ月間しかないと考えると、この結果は悪くないだろう。

Source

コメントを残す