世界のリソグラフィ装置業界の巨人として、市場シェアの90%以上を占めるASMLは、High-NA技術に基づく新世代のEUVリソグラフィ装置を発売しようとしている。この新しいEUVリソグラフィ装置の出現は、半導体業界に大きな衝撃を与える事になるだろう。ASMLの最高技術責任者であるMartin van den Brink氏は、 High-NA技術はおそらくEUVリソグラフィ技術の終わりとなると述べている。

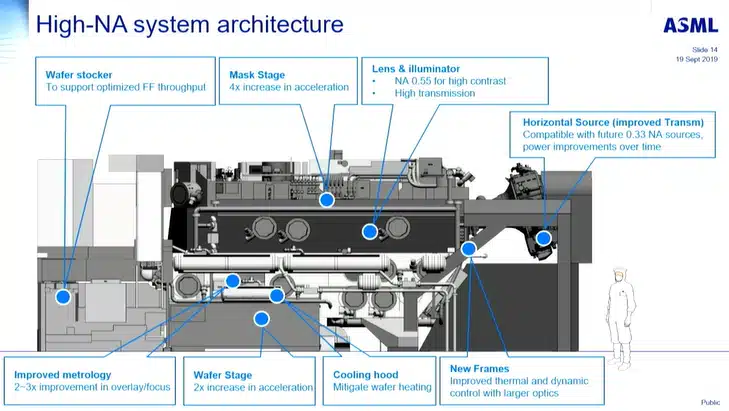

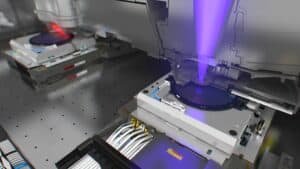

NAとは、光学系の開口数で、光の入射角度を示す。より大きなNAのレンズを使用することで、より小さな構造をプリントすることができ、より高度なチップ製造プロセスを提供することができる。現在のEUVリソグラフィ装置には0.33NAの光学デバイスが使用されているが、High-NA技術ではさらに0.55NAまで開口率を高めることが可能だ。

しかし、物理的な制約から、High-NAは更なる発展が困難とされている。例えば、High-NAミラーは前世代の2倍の大きさで、20ピコメートル(1000ピコメートル=1ナノメートル)以内に平坦化する必要がある。検証作業は真空容器で行う必要があり、検証容器は現在、光学大手Carl Zeissが担当している。その他、放熱、光の回折、光路の閉塞、体積などの問題もあり、NAの技術をさらに向上させることは困難である。

ASMLのHigh-NA技術に基づくEUVリソグラフィ装置は2024年に納入される予定で、2nm以下のプロセスで使用され、EUVリソグラフィ路線は終了するとも言われている。実は、チップ技術のさらなる発展を制約するのは、リソグラフィ装置ではなく、原料シリコンの問題になるのだ。

シリコン原子の共有結合半径は0.11nm。リソグラフィ装置の技術が1nmまで発展すると、原子間の距離が近すぎるために量子トンネル効果が発生し、電子が絶縁層を通過しやすくなり、半導体が完全な導体になる、つまり0と1を表す機能を失うこともシリコンベースのチップにとって避けられないジレンマなのである。

1nmの限界をさらに突破するために、シリコン以外のチップ材料を探すことも一つの方向性になってきた。例えば、金属ビスマス(Bi)を2次元材料のコンタクト電極に使うと、抵抗値が大幅に下がり、電流を増やすことができるため、将来的に半導体の1nmプロセスの実現につながると、科学誌『Nature』に掲載されたことがある。その他、カーボンナノチューブやシリコンカーバイドなども代替材料となる。しかし、どの材料も最初に直面する問題はコストが高すぎることなので、1nmがチップ開発の分水嶺になることも一つの可能性として考えられる。1nmを突破した後も、チップメーカーは長い間、改良を重ねるしかないだろう。

チップ開発が徐々に終了することは、先端チップを製造する事が出来ない中国や日本の業界にとっては逆に朗報でもある。国産チップはまだ追随者の域を出ていないと認めざるを得ない。

このままチップがムーアの法則に従うのであれば、追いつくためにはより多くの技術とリソースが必要になることは間違いない。しかし、チップの限界である1nmが徐々に到来すれば、TSMC、Samsung、Intelなどのリーダーのペースも減速せざるを得ず、後続のメーカーとの差が縮まる可能性もあるだろう。

同時に、EUVリソグラフィ装置にせよ、炭素系チップにせよ、限界に達するということは、代替品を見つけなければならないことを意味する。とはいえ、Intelなどの半導体企業は既にフォトニクスや量子コンピュータなど、その代替技術の開発にも着手している。

Source

- Bits&Chips: Hyper-NA after high-NA? ASML CTO Van den Brink isn’t convinced

- Semiconductor Engineering: Multi-Patterning EUV Vs. High-NA EUV

コメントを残す